# **CHAPTER 3**

## Double Gate Junctionless FET with SiC substrate

## Contents

- 3.1 Introduction

- 3.2 Why Junctionless FET?

- 3.3 Silicon Carbide (SiC) as Substrate for High-Power Applications

- 3.4 DG-SiCJLT: A Symbiosis of Material Excellence and Device Innovation

- 3.5 Literature Review on DG-SiCJLT

- 3.6 Device Architectures and Simulation Set-up

- 3.7 Results and Discussions

- 3.8 High-Temperature Performance of DG-SiCJLT and P<sup>+</sup>-SiCJLT

- 3.9 Comparison with Devices Featuring Embedded Pockets in Substrate near Source/Drain Contact

- 3.10 Fabrication Steps for The Proposed  $P^+$ -SiCJLT

- 3.11 Summary

Bibliography

### **3.1. Introduction**

As heralded by the IEEE International Roadmap for Devices and Systems (IRDS), the low-power semiconductor industry continuously strives to increase performance by packing more and more transistors in a single chip [1]. On the other hand, the high-power or power electronics industry aims toward higher power capacity for their chips. However, Silicon still holds the significant market share for high-voltage and low-power transistors. This is because of its excellent interface quality with SiO<sub>2</sub>, low-cost substrate, mature processing technology, and decades of research and development. In the low-power electronics market, the dimension of the traditional transistors approached physical limits (in terms of gate control, output current, capacitance, power/performance ratio, etc.) as they were scaled down, and performance and reliability suffered. The industry has since moved to non-planar fully depleted (FD) multi-gate MOSFETs (MugFETs) such as FinFETs, for sub 20 nm ultra-large-scale integration (ULSI) applications, allowing dimensional scaling and higher reliability, thus manufacturing integrated circuits with higher packing density and better performance [2, 3]. Although such a transistor has great performance metrics, it has abrupt source and drain junctions, which poses fabrication complexities in doping profiles, thus preventing further scaling down, or intricate integration with other CMOS technologies. Junctionless transistors (JLT), on the other hand, have homogeneous and uniform doping profiles. Combining this advantage along with many others (better short channel control, negative bias thermal instability, lesser random telegraph-noise and 1/f noise, low thermal budgets, etc.) depicts the potential of JLTs as a better fit for memory applications, IoT technology, etc. than FD MOSFETs [4-7]. Despite these advantages, a JLT isn't commercialized yet for daily life applications, because of relatively intricate fabrication techniques (e.g., ~5-10 nm substrate thickness with uniform, high doping) and some electrical performance constraints (e.g., inferior transconductance compared to IM MOSFETs). However, if tremendous performance advantages can be forecasted, these fabrication-related challenges and low drain current can be met over time, just like in the case of FinFETs.

The double-gate junctionless field-effect transistor (DG-JLT) on silicon carbide (SiC) substrate is a promising development in semiconductor technology for its superior performance and scalability over traditional transistors. SiC substrates offer a number of benefits, such as increased electron mobility and thermal conductivity, which improve

device dependability and efficiency [8, 9]. The transistor's double gate design provides exact electrostatic control over the channel, resulting in improved transistor properties like a high ON-OFF current ratio and a low leakage current.

## 3.2 Why Junctionless FET?

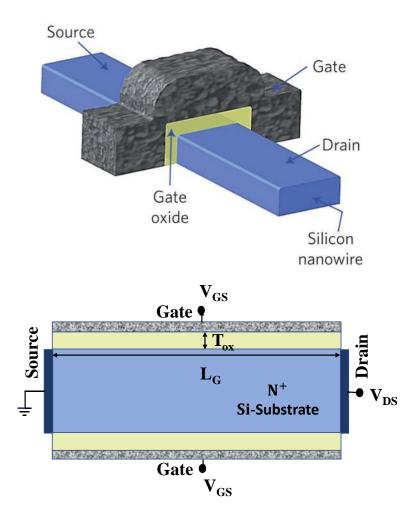

In 2010, researchers at the Tyndall National Institute, led by Dr. Jean-Pierre Colinge and his team, made a significant breakthrough in semiconductor technology by developing Junctionless Transistors (JLTs) [4]. Unlike in conventional transistor, JLT has no PN junction in source-channel-drain path. This invention represented a break from the conventional method of designing transistors, which relied on doping concentrations (source-channel and channel-drain) within the semiconductor material. Schematic of an n-channel nanowire transistor shown in Fig. 3.1, this seemingly straightforward change produced a device that outperformed conventional MOSFETs in several important ways.

Fig. 3.1: Schematic of an n-channel nanowire transistor [4].

There are numerous important advantages to JLTs not having a PN junction. Firstly, JLTs are more scalable than MOSFETs. The adverse impacts of short-channel effects on MOSFETs cause leakage current problems and performance deterioration as device dimensions decrease. Alternatively, due to the absence of the PN junction and the associated depletion zone in JLTs, they inherently exhibit reduced susceptibility to these effects [10]. This makes it possible to keep shrinking JLTs to some extent and therefore push the limits of miniaturization.

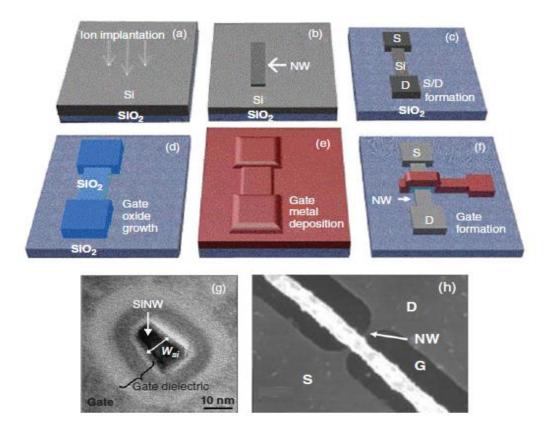

Secondly, the fabrication process is streamlined due to the uniform doping in JLTs (see Fig. 3.2). Unlike MOSFETs, where the creation of PN junctions necessitates precise control over doping concentrations and involves high-temperature diffusion or implantation stages, JLTs achieve PN junction functionality without these requirements. This may result in comparatively cheaper production costs in addition to reducing the complexity of fabrication.

Fig. 3.2: Illustrated Procedure for Fabricating NWJLFETs [11]: (a) ion implantation of SOI film, (b) Defining the nanowire channel, (c) Forming contact pads for the source and drain, (d) Growing or depositing the gate oxide layer, (e) Deposition of the gate metal, (f) Defining the gate electrode [12], (g) Examining the fabricated NWJLFET through a cross-sectional TEM image [13], and (h) Observing the fabricated nanowire metal-oxide-semiconductor field-effect transistor (NWMOSFET) through a bird's-eye SEM image [14].

Thirdly, JLTs have the ability to enhance the functionality of devices. In contrast to MOSFETs, JLTs exhibit volume inversion. Their capability for better  $I_{ON}/I_{OFF}$  ratio and lower leakage current makes JLT a better device for lower power application.

In addition, JLTs outperform MOSFETs in terms of resistance to hot carrier effects. Electrons with high energy can break free from their channels and infiltrate the gate oxide, causing damage to the device. This phenomenon is known as hot carriers. JLTs' homogeneous doping profile reduces the production of hot carriers and lesser surface scattering, increasing the longevity and dependability of the device.

### 3.3 Silicon Carbide (SiC) as Substrate for High-Power Applications

The limitations of Silicon, especially its narrow bandgap, reduced heat conductivity, and decreased electron mobility, limit its usefulness in high-frequency and high-power applications. In contrast, SiC has a much wider bandgap (around 3.2 eV for 4H-SiC), which allows devices to withstand much higher voltages before breaking down [7]. This results in a significant increase in SiC-based DG-JLTs' breakdown voltage, which makes them suitable for use in power electronics applications such as electric car converters and switch-mode power supplies. SiC, as opposed to Si, also has better heat conductivity. Because of their improved capacity to dissipate heat effectively, DG-JLTs can withstand higher power densities without experiencing performance degradation [15]. This is especially useful in high-power switching applications where a considerable amount of heat generation is unavoidable. In terms of electron mobility, SiC performs better than Si, even after controlling temperature and breakdown voltage. A Dual-Gate Silicon Carbide Junctionless Transistor (DG-SiCJLT) channel experiences faster current flow due to SiC's increased electron mobility. Improved device performance results in reduced signal distortion and faster switching rates in high-frequency applications such as microwave circuits and radio frequency (RF) amplifiers [16].

Another strong benefit of SiC is its chemical stability [17]. SiC is extremely resilient in adverse environments, in contrast to Si, which degrades at high temperatures [18]. Because of this feature, DG-SiCJLTs are ideally suited for demanding applications in the aerospace and military industries, where equipment must perform dependably in harsh environments [19].

## **3.4 DG-SiCJLT: A Symbiosis of Material Excellence and Device** Innovation

A DG-JLT's channel experiences faster current flow due to SiC's increased electron mobility. The DG-SiCJLTs' promise is further highlighted by the DG design. A narrow, evenly doped channel section is positioned between two gate electrodes in the core construction of a DG-JLT.

Metals and high-k dielectrics are two examples of the materials that can be used to create these gates. By creating an electric field, applying a voltage to the gates modifies the conductivity of the channel. While a negative voltage builds up charges at the channel surface, increasing current flow, a positive voltage on the gates depletes the channel and decreases current flow [20]. Furthermore, by reducing the impact of shortchannel effects, the double-gate design allows DG-SiCJLTs to be scaled up even further for even higher density integration. Numerous benefits arise from the novel DG-JLT architecture in conjunction with the superior material quality of SiC. First of all, DG-SiCJLTs are perfect for high-power switching applications because of their extraordinarily high breakdown voltage. Second, effective heat dissipation is made possible by their greater thermal conductivity, which is essential for high-power density operation. Thirdly, enhanced performance in high-frequency applications and quicker switching speeds are a result of SiC's high electron mobility. Fourth, SiC's chemical stability guarantees dependable performance even in challenging conditions. Ultimately, the DG architecture minimizes short-channel effects, provides steeper subthreshold swing, and allows for better control over current flow, opening the door to further downsizing [21].

#### 3.5 Literature Review on DG-SiCJLT

In recent years, besides Silicon, wide bandgap (WBG) semiconductors, namely, gallium nitride (GaN), ( $E_g \sim 3.4 \text{ eV}$ ), silicon carbide (SiC) ( $E_g \sim 3.3 \text{ eV}$ ) and  $\beta - Ga_2O_3$  ( $E_g \sim 4.5-5.3 \text{ eV}$ ) have received the limelight because of their high breakdown, high-frequency operation, etc. [18, 22, 23]. SiC exhibits a higher figure-of-merit (FOM) value, w.r.t. Silicon in the common metrics (Baliga FOM, Johnson FOM, Keyes FOM, Huang HCAFOM, Shenai et al., etc.[8, 9, 15, 16]. Although these FOM show that SiC could be a viable choice for power electronics switches, one should be careful about using the FOMs. It can be easily seen that each FOM is designed for a specific application such as high power, high voltage, or high temperature.

Unfortunately, different materials (e.g., Si, GaN, SiC) and devices (e.g., VDMOS, LDMOS, HEMT) are affected differently due to their dimensions, operating conditions, defects, etc. Therefore, an analytical framework for material-device-circuit-system simulations based on early-stage products is needed to assess performance. Mahajan et al. [24] reported an analytical model of an intrinsic Safe Operating Area (SOA) for the selection of a WBG semiconductor that accounts for the self-heating (SH) effect, substrate geometry, basic device parameters (mobility, thermal conductivity, critical electric field, etc.) and trap-induced degradation for applications in a modern power electronics application, that is more reliable than the traditionally used material specific FOMs. The higher the SOA, the higher the performance of a power electronics switch. Based on the analytical framework, the authors show that SiC has a higher SOA, compared to Silicon. In addition, SiC device fabrication technology is quite mature. Among all polymorphs of SiC, transistors with 4H-SiC have better potential in highpower electronics because of their high carrier mobility ( $\mu$ ) (500/50 cm<sup>2</sup>/Vs-s for electron/hole, low ON-resistance, faster-switching capability, higher thermal conductivity, etc. [7, 18, 22]. In addition, 4H-SiC (referred to as SiC, hereafter) has high mechanical strength (Young's modulus of ~400-450 GPa), which makes SiC suitable for high-T, high-power electronics and harsh environmental conditions [25]. Therefore, we have chosen SiC for our analysis, in this paper. Several devices/electronics based on SiC are under development, which requires metallization, interfacing, and co-integration with oxide & other materials for SiC devices for the mass commercial market [26].

SiC-based JLT suppresses the impact of interface traps, thus avoiding the need for a counter doping and annealing process to lower the band-to-band (BTBT) tunneling across the channel direction [27]. It has been demonstrated that by placing two P<sup>+</sup> regions adjacent to source/drain regions in a JLT (SD<sub>Pocket</sub>-SiCJLT), the volume depletion can be improved [28]. With P<sup>+</sup> pockets in the oxide region for  $\beta - Ga_2O_3$ JLT, volume depletion improves [29]. However, JLT possesses some inherent limitations. JLT has two modes of operation: inversion and depletion. The channel of a JLT may be fully depleted either by applying a negative voltage (for NMOS) to turn it off or applying a high gate WF (P-type). Also, the channel has to be very thin (~5-10nm), leading to very low ON-current and often unreliable performance due to extreme fabrication constraints. The channel is highly doped to enhance  $I_{ON}$ . Depletionmode transistors require additional circuitry and high-power dissipation for switching applications in power electronics which increases the power budget, and hence enhancement-mode transistors are highly desirable. This work proposes an enhancement mode double-gate SiC JLT, with an embedded  $P^+$  layer in the oxide region for lower OFF-state current and efficient volume depletion. We thoroughly explore the DC and AC performances of the device ( $P^+$ -SiCJLT) and compare it with a similar dimensional SiC JLT without an embedded  $P^+$  layer and discuss the advantages and disadvantages. In addition, we also compare the  $P^+$ -SiCJLT with a SiCJLT with  $P^+$  pockets adjacent to the source/drain region (SD<sub>Pocket</sub>-SiCJLT).

#### **3.6 Device Architectures and Simulation Set-up**

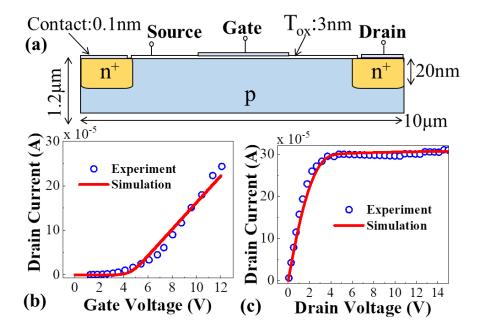

The traditional SiC MOSFET was calibrated with an experimental device by Mudholkar et al. [30, 31] considering channel thickness of 1.2  $\mu$ m, channel/(source/drain) doping concentration of  $10^{17}/(9 \times 10^{19})cm^{-3}$ , gate oxide thickness of 3 nm with SiO<sub>2</sub> as gate oxide material and a very thin layer of gold (0.1nm) for source, gate, and drain contacts as SiC JLT is not fabricated yet to the best of our knowledge. Specifically, a mesh with 5 nm length and 2 nm width was used near the channel/source-drain regions to ensure accuracy in capturing detailed device features. The mesh was optimized to balance computational efficiency with precision, focusing on areas with steep gradients where accurate simulation is crucial.

Fig. 3.3: Calibrated TCAD simulation with the (a) experimental device of (b) transfer characteristics at  $V_{DS} = 50mV$  (c) output characteristics at  $V_{GS} = 6V$  for  $T_{OX}$  (SiO<sub>2</sub>)=3 nm, N<sub>A</sub>=10<sup>17</sup> cm<sup>-3</sup>, N<sub>source,drain</sub>=9×10<sup>19</sup> cm<sup>-3</sup>, T<sub>SiC</sub>=1.2 µm, L=20 µm [30, 31].

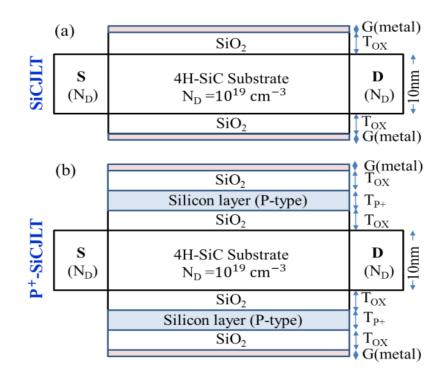

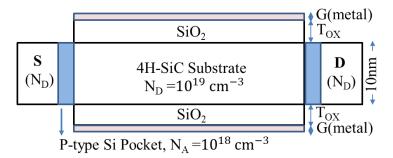

Grid statistics were adjusted to ensure convergence and minimize numerical errors, providing reliable calibration data. The Fermi–Dirac statistics, Shockley–Read–Hall recombination, and Auger recombination were included. The mobility of SiC has been determined by fitting to be 210 cm/V-s. The mobility degradation is due to scattering at the  $4HSiC - SiO_2$  interface and doping and transverse field dependencies of mobility were taken care of by the inversion and accumulation-layer mobility (IalMob) model. The Canali model was used for velocity saturation. All simulations were carried out using Sentaurus TCAD version R-2020.09-SP1 by Synopsys Inc. [32]. The transfer and output characteristics of the TCAD model are calibrated with experiments, as shown in Fig. 3.3(b) and 3.3(c). A SiC JLT can be designed using the calibrated parameters, as shown in Fig. 3.4(a), demonstrating higher performance than traditional MOSFET [33]. We use these parameters to introduce a P<sup>+</sup>-SiCJLT device, as shown in Fig. 3.4(b). The substrate is 4H-SiC, and the oxide material is SiO<sub>2</sub>. The channel/source(drain) length of the device was taken as 100/20nm, source-drain doping concentration (N<sub>D</sub>) as  $10^{19}$  cm<sup>-3</sup>, and gate work function (WF) as 5.1eV.

Fig. 3.4: Block diagram (a) SiCJLT (without the P+ layer in the oxide region) and (b) P+-SiCJLT.

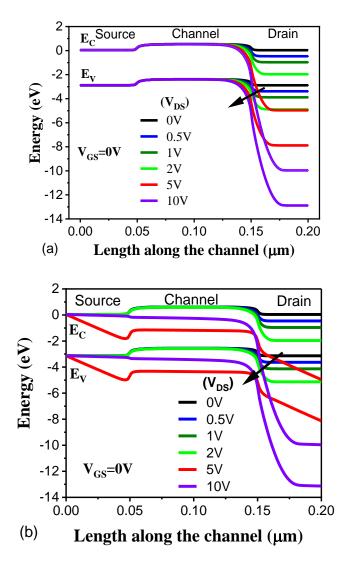

Without the P+ layers in Fig. 3.5(a), the energy bands (conduction and valence bands) across the channel exhibit more gradual transitions. The conduction band  $E_C$  near the source and drain shows a weaker potential barrier, leading to higher leakage currents, especially at lower gate voltages. In contrast, with the P+ layers, the energy bands shift, creating steeper transitions near the source and drain. This shift results in better confinement of carriers in the channel, as the conduction band  $E_C$  shows a more substantial rise, forming a higher potential barrier that reduces leakage.

Fig. 3.5: Energy band diagram of (a) SiCJLT and (b) P<sup>+</sup>-SiCJLT at  $V_{DS} = 0,0.5V,1V,2V$  5V, 10V and  $V_{GS} = 0V$ .

At  $V_{DS}$ =0.5V and  $V_{GS}$ =0V, the conduction band with the P+ layer shows a potential difference of approximately 1.5 eV between the source and drain compared to 1.0 eV in the device without the P+ layers. This 0.5 eV increase significantly improves carrier confinement.

The addition of P+ layers also affects the vertical energy profile across the silicon thickness. With the P+ layers, there is stronger band bending at the surface near the source and drain, which helps suppress the off-state leakage. Without the P+ layers, the conduction and valence bands are more uniformly distributed across the silicon thickness, resulting in weaker electrostatic control.

At  $V_{DS}$ =1V and  $V_{GS}$ =0V, the energy barrier in the vertical direction increases by approximately 0.7 eV when the P+ layers are included. This increase enhances the overall electrostatic control, leading to a better subthreshold slope and improved performance at higher temperatures.

The inclusion of P+ layers enhances device performance by creating sharper band bending near the source and drain, increasing electrostatic control, reducing leakage, improving the subthreshold swing, and enhancing the high-temperature stability of the device. The numerical shifts observed in the conduction band energies confirm the improvements provided by the P+ layers.

An embedded layer of Silicon in the SiO<sub>2</sub> is added to the proposed device. The embedded P<sup>+</sup> material (Si) has a thickness ( $T_{P+}$ ) of 2-4 nm and a P<sup>+</sup> (boron) doping concentration ( $N_{P+}$ ) of  $10^{15} - 10^{18} cm^{-3}$  unless otherwise mentioned. The energy band diagram of the P<sup>+</sup>-SiCJLT at  $V_{GS} = 0V$  and  $V_{DS} = 0,0.5V,1V,2V,5V$ , and 10V) are shown in Fig. 3.5(b). With an increase in  $V_{DS}$ , the conduction band of the drain and valance band of the channel overlapped, resulting in better electrostatics for the device. As evident, because of the P<sup>+</sup> pockets, the device exhibits full depletion in the OFF-state. The bias condition at the OFF state is  $V_{GS} = 0$  V and a small drain voltage, typically  $V_{DS} = 50$  mV. The physical reason for full depletion in the OFF state is the presence of the P+ pockets, which enhance the electric field across the channel, effectively depleting carriers even at zero gate bias. This leads to a wide depletion region, preventing current flow and ensuring low leakage. For lower  $V_{DS}$ , there is no band overlapping, meaning that the device has higher tunnel width and hence offers lower leakage current, making the device a better fit for high voltage applications.

In this work, the term "P+" was used more generally to describe the p-type silicon layer incorporated in the top and bottom gate stacks of the device. The intention was to highlight that this layer has a higher doping concentration compared to typical intrinsic or lightly doped p-type regions.

However, it is acknowledged that using the term "P+" may have led to some confusion, as the doping concentrations in the range specified do not achieve degenerate doping levels. The doping concentrations used  $10^{15} - 10^{18} cm^{-3}$  were chosen to optimize the electrostatic control of the device while maintaining a balance between performance and fabrication feasibility. The layer should more accurately be referred to as a "moderately doped p-type layer" rather than "P+," as the doping levels do not reach the degenerately doped regime.

#### **3.7 Result and Discussion**

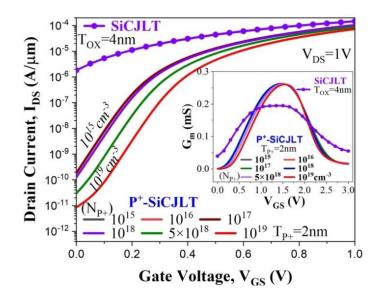

The transfer characteristics of a P<sup>+</sup>-SiCJLT for P<sup>+</sup> layer doping concentration  $(N_{P+})$ of  $10^{15}$ ,  $10^{16}$ ,  $10^{17}$ ,  $10^{18}$ ,  $5 \times 10^{18}$ , and  $10^{19}$  cm<sup>-3</sup> at a P<sup>+</sup> layer thickness ( $T_{P+}$ ) of 2 nm and its comparison with the equivalent dimension SiCJLT (i.e.,  $T_{OX} = 4$ nm) is shown in Fig. 3.6. It is seen that with an increase in doping concentration of the P+ layer beyond  $10^{18}$  cm<sup>-3</sup>, the electrostatics is improved. For example, from a N<sub>P+</sub> shift from  $10^{18}$  cm<sup>-3</sup> to  $10^{19}$  cm<sup>-3</sup>, there is an I<sub>OFF</sub> improvement of slightly more than one decade. However, for  $N_{P+}$  change from  $10^{15}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup>, there is negligible change in both  $I_{OFF}$  and  $I_{ON}$ . Therefore, even though electrostatics is better at  $N_{P+} =$  $10^{19}$  cm<sup>-3</sup>, we have considered N<sub>P+</sub> of  $10^{18}$  cm<sup>-3</sup> for all simulations to have minimum scattering as well as to see the worst-case scenario of electrostatics. P+-SiCJLT in a double gate architecture helps in realizing an effective volume depletion region. A double-gate P<sup>+</sup>-SiCJLT exhibits enhancement mode operation, advantageous for power electronics switching applications. On the other hand, SiCJLT exhibits a depletion mode operation. Depletion mode operation requires extra circuitry, which increases the losses as well as the cost of a power electronic switch. With an increase in the value of  $N_{P+}$ , better gate control and  $I_{ON}/I_{OFF}$  is expected. With lower  $I_{OFF}$ , the low WF gate metal can be chosen. In Silicon-based JLT, a p-type gate WF (>5eV) and an ultra-thin semiconductor substrate thickness of ~5-10nm are required to fully deplete the channel. Such smaller thicknesses with uniform doping with low surface roughness are difficult and costly. Therefore, multiple WF can be selected according to the application for double-gate P<sup>+</sup>-SiCJLT. The inset of Fig. 3.6 shows the transconductance  $(G_m)$  of a P<sup>+</sup>-SiCJLT for different doping concentrations at a P<sup>+</sup> layer thickness of 2 nm. We compare this to an equivalent SiCJLT device. We find that for specified device dimensions and electrical biases ( $V_{GS} = \sim 0.8 - 2.4V$ ), the P<sup>+</sup>-SiCJLT better transconductance.

Fig. 3.6: Transfer characteristics of P+-SiCJLT for  $N_{P+} = 10^{15}$ ,  $10^{16}$ ,  $10^{17}$ ,  $10^{18}$ ,  $5 \times 10^{18}$ , and  $10^{19}$  cm<sup>-3</sup> and  $T_{P+} = 2$ nm, L = 100nm. This is compared with equivalent dimension SiCJLT at  $T_{OX} = 4$ nm. The inset of Fig. 3.6 shows the transconductance for the devices.

The  $I_{DS}$ - $V_{GS}$  characteristics were obtained using a double-gate configuration for the P<sup>+</sup> SiCJLT. The applied bias on the P<sup>+</sup> layer in the gate stack is the same as the gate voltage,  $V_{GS}$ . The  $I_{DS}$ - $V_{GS}$  characteristics remain almost unchanged over the doping range of  $1 \times 10^{15} - 1 \times 10^{18} \text{ cm}^{-3}$  because, within this range, the doping concentration is not high enough to significantly alter the electrostatic control of the channel.

For doping concentrations  $\geq 1 \times 10^{18} \ cm^{-3}$ , the increased carrier density in the P<sup>+</sup> layer leads to enhanced scattering and reduced carrier mobility, which physically explains the observed decrease in  $I_{DS}$ .

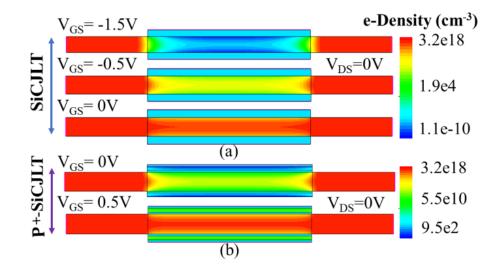

With P<sup>+</sup>-SiCJLT, effective volume depletion can also be tuned as shown in Fig. 3.7(b). However, to deplete a similar dimensional SiCJLT, a high negative voltage ~ (-1.5V) is required (Fig. 3.7(a)). At a moderately higher  $V_{GS}$  (> $V_{TH}$ ), current flows in the center of the substrate in a JLT [4], and current is not hampered by Si – SiO<sub>2</sub> interface. This is in contrast to an IM MOSFET, where the current flows close to the Si/SiO<sub>2</sub> interface, which gives rise to several reliability issues like mobility degradation due to surface scattering, and interface defects leading to hot carrier degradation, and negative bias temperature instability, etc. P<sup>+</sup>-SiCJLT, therefore, avoids these reliability issues as well. In addition, a P<sup>+</sup>-SiCJLT has a near-zero vertical electric field in the ON-state, and thus undergoes negligible mobility degradation in ON-state [34].

Fig. 3.7: E-density at  $V_{DS} = 0V$  for (a) SiCJLT at  $V_{GS} = -1.5V$ , -0.5V, 0V, and (b) P<sup>+</sup>-SiCJLT at  $V_{GS} = 0V$ , 0.5V and  $N_{P+} = 10^{18}$  cm<sup>-3</sup> for the same device dimensions as Fig. 3.4.

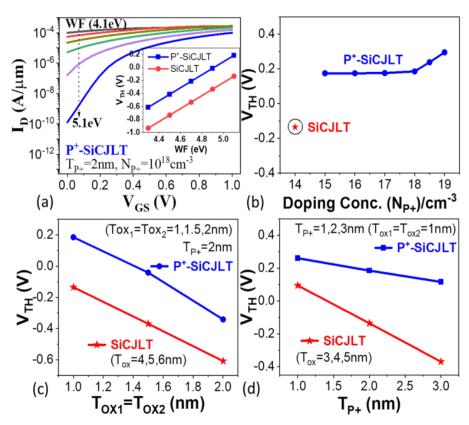

### 3.7.1 Threshold Voltage Engineering

P<sup>+</sup>-SiCJLT can be engineered to achieve customizable  $V_{TH}$  and higher performance, according to specific applications. Fig. 3.8(a) shows that better volume depletion can be achieved with higher WF, which will eventually have better  $I_{ON}/I_{OFF}$ . The inset of Fig. 3.8(a) shows that the  $V_{TH}$  increases with an increase in WF. Also, P<sup>+</sup>-SiCJLT has a higher  $V_{TH}$  than SiCJLT by about 400mV, despite using the material with a similar WF. Currently, there is no analytical or empirical equation in the literature to aid the design the SiC junctionless FETs with varying threshold voltages to the best of our knowledge. Therefore, based on our rigorous simulations, we propose the following equations that predict the  $V_{TH}$ , achieved using linear curve fitting the simulation data. Please note that, these equations are not based on any theoretical model but on our simulation, to aid the circuit designer in designing a transistor best suited to a particular application. The  $V_{TH}$  (V) of SiCJLT and P<sup>+</sup>-SiCJLT, at a given WF is given by

$$V_{TH} \text{ (SiCJLT)} = WF - 5.23 \tag{3.1}$$

$$V_{TH}$$

(P<sup>+</sup>- SiCJLT) = WF - 4.91 (3.2)

with 4 < WF <5.2. The  $V_{TH}$  can also be tuned by changing the doping concentration of the P<sup>+</sup> layer ( $N_{P+}$ ). With an increase in  $N_{P+}$ , OFF-state current and  $I_{ON}/I_{OFF}$  improves and  $V_{TH}$  increases as seen in Fig. 3.8(b). Also,  $V_{TH}$  can be tuned by changing the oxide thickness. A device with thinner gate oxide has a higher  $V_{TH}$  as shown in Fig. 3.8(c). It should be noted that such thin gate oxides may be leaky due to fabrication constraints. If  $T_{OX1} = T_{OX2}$ , the  $V_{TH}$  of SiCJLT and P<sup>+</sup>-SiCJLT can be written as:

$$V_{TH}$$

(SiCJLT) = -0.47× $T_{OX1}$  (=  $T_{OX2}$ ) + 0.33 (3.3)

$$V_{TH} (P^+-SiCJLT) = -0.52 \times T_{OX1} (= T_{OX2}) +0.72$$

(3.4)

with 1 nm  $< T_{OX1}=T_{OX2} < 3$  nm. The P<sup>+</sup>-SiCJLT provides another option to tune the  $V_{TH}$  of the device by changing the P<sup>+</sup> layer thickness. Simulations of devices with  $T_{P+}$  of 1nm, 2nm, and 3 nm and  $N_{P+}$  of  $10^{18}$  cm<sup>-3</sup>, are shown in Fig. 3.8(d). Equations (3.1-3.4) will be helpful in the Design Technology Co-Optimization (DTCO) of similar transistors. The development of these equations provides a solid foundation for understanding and predicting the threshold voltage behavior of P+-SiCJLT and SiCJLT devices in a specific geometry. This allows for easier integration into circuit simulations and provides insights into how different parameters affect device performance. By fine-tuning these relationships, we can now better model the behavior of junctionless transistors in power electronics applications, ensuring more accurate performance predictions. However, because these equations were tailored to a specific set of device

Fig. 3.8: P<sup>+</sup>-SiCJLT is simulated with  $N_{P+} = 10^{18}$  cm<sup>-3</sup>, and  $T_{P+} = 2$ nm for (a)  $I_{DS}$  with gate voltage for WF=4.1-5.1eV. Inset of this Fig. also shows the  $V_{TH}$  change with WF (b)  $V_{TH}$  change with  $N_{P+}$  (c)  $V_{TH}$  change with  $T_{OX1} = T_{OX2} = 1$  to 2 nm (d)  $V_{TH}$  change with  $T_{P+} = 1$  to 3 nm. The characteristics are compared with equivalent dimension SiCJLT.

dimensions, they may not directly apply to devices with significantly different geometries (e.g., variations in channel length or width) without recalibration. The device with a thinner P<sup>+</sup> layer exhibits improved volume depletion and therefore has better electrostatics. Therefore P<sup>+</sup>-SiCJLT provides the capability to tune the  $V_{TH}$ , in several different ways (P<sup>+</sup> layer thickness and P<sup>+</sup> layer doping) in addition to the traditional  $V_{TH}$  tuning approaches (WF,  $T_{OX}$ ). This can provide the engineers with multiple fabrication options if a limit is reached with one parameter. Therefore the P<sup>+</sup>-SiCJLT increases the scalability of JLTs.

The impact of parameters such as  $T_{OX1}$  and  $T_{OX2}$  on the electric field distribution and channel depletion were carefully analyzed. For instance, thinner gate oxides increase gate capacitance, which in turn raises  $V_{TH}$  by requiring a stronger gate field to invert the channel. The inclusion of the P+ layer in the P<sup>+</sup>-SiCJLT increases  $V_{TH}$  by depleting the channel more effectively.  $T_{OX1}$  and  $T_{OX2}$  were defined based on how they affect gate control and depletion width. These parameters were adjusted to optimize electrostatic control and performance for the device applications explored in this study.

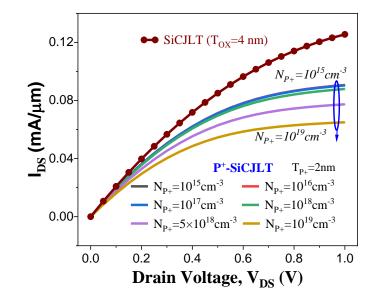

Fig. 3.9: Drain current with drain voltage for P<sup>+</sup>-SiCJLT for  $N_{P+} = 10^{15}$  cm<sup>-3</sup>,  $10^{16}$  cm<sup>-3</sup>,  $10^{17}$  cm<sup>-3</sup>,  $10^{18}$  cm<sup>-3</sup>,  $5 \times 10^{18}$  cm<sup>-3</sup>,  $10^{19}$  cm<sup>-3</sup> at  $T_{P+} = 2$ nm. This is compared with equivalent dimension SiCJLT.

#### **3.7.2** Lower Output Current

Fig. 3.9 shows the output characteristics of a P<sup>+</sup>-SiCJLT for different P<sup>+</sup> doping concentrations, and the same is compared with equivalent dimension SiCJLT. P<sup>+</sup>-SiCJLT has lesser  $I_{DS}$  than a SiCJLT. The primary physical mechanism for  $I_{DS}$  degradation with increasing P<sup>+</sup> layer doping at higher  $V_{DS}$  in P+ SiCJLT is the

enhanced depletion of the channel. As the P<sup>+</sup> doping increases, the built-in electric field becomes stronger, leading to a more significant depletion of carriers in the channel. This reduction of available carriers diminishes the current drive capability of the device, especially at higher drain voltages (e.g.,  $V_{DS} = 2V$ ), where the channel is further pinched off. The result is a reduced  $I_{DS}$ , not primarily due to scattering, but due to the more effective carrier depletion induced by the higher P<sup>+</sup> doping.

### 3.8 High-Temperature Performance of DG-SiCJLT and P<sup>+</sup>-SiCJLT

With the proposed P<sup>+</sup>-SiCJLT, the applicability of the JLTs will be further stretched because of the advantages ((increased scalability, enhancement mode operation, multiple ways to tune  $V_{TH}$ , etc.) The proposed P<sup>+</sup>-SiCJLT is also advantageous in terms of intrinsic gain at room and even high T.

#### **3.8.1 Drain Current at High-Temperature**

Usually, with a rise in temperature (T), the threshold voltage ( $V_{TH}$ ) falls and hence the drain current rises for all transistors. In an inversion mode device, though  $V_{TH}$ reduction increases  $I_D$ , mobility reduction due to phonon scattering eventually decreases the drain current [5, 35, 36]. In a JLT, with an increase in T, impurity scattering (mobility,  $\mu \propto T^{3/2}$ ) and phonon scattering ( $\mu \propto T^{-3/2}$ ) compensate for each other at a particular  $V_{GS}$  called zero temperature coefficient (ZTC) [37], and therefore, mobility reduction with higher T is lesser in a JLT compared to an IM MOSFET. Therefore, in JLTs, reduction in mobility with temperature is much lower than other types of transistors, and hence current increases marginally with a monotonous trend [38]. In conclusion, JLT shows better  $I_{ON}$  and  $I_{OFF}$  and hence superior  $I_{ON}/I_{OFF}$  than conventional transistors even at higher temperatures, making the device suitable for higher temperature applications.

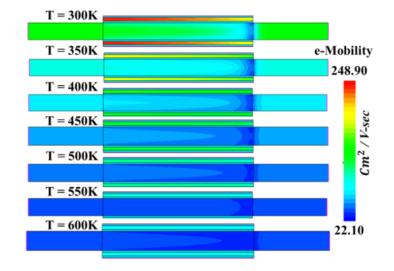

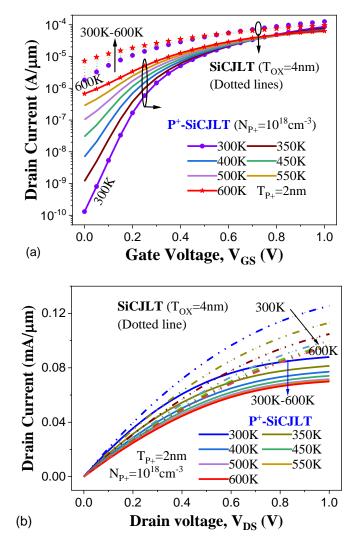

There is a degradation of e-mobility with T increase as shown in Fig. 3.10. The transfer characteristics of a P<sup>+</sup>-SiCJLT for a T range of 300K-600K and its comparison with SiCJLT are demonstrated in Fig. 3.11(a). With an increase in T,  $I_{OFF}$  degrades for both the devices. The  $I_{ON}$  is very marginally improved with an increase in T, unlike in conventional transistors. Therefore,  $I_{ON}/I_{OFF}$  is better for P<sup>+</sup>-SiCJLT even at a higher T.

Fig. 3.10: Electron mobility for P<sup>+</sup>-SiCJLT at T = 300K - 600K at 50K step size and  $N_{P+} = 10^{18}$  cm<sup>-3</sup>,  $T_{P+} = 2$ nm.

SiCJLT has a higher output current than P+-SiCJLT and degrades with T as shown in Fig. 3.11(b). The ON-state current of a JLT is slightly lesser than conventional transistors because of its high doping concentrations ( $\sim 10^{18} - 10^{19} \text{ cm}^{-3}$ ) in the channel region. However, it is almost comparable, with an addition of other advantages. On the same note, SiC-MOSFET with two P-N junctions has a better current than SiC-JLT. The MOSFET typically shows a higher current drive for the same dimention as measured from TCAD simulation, capability due to the presence of the two P-N junctions. At  $V_{GS}=5 V$  and  $V_{DS}=10 V$ , the  $I_{DS}$  for the SiC-MOSFET was approximately 15 mA. The MOSFET showed more significant degradation in performance at elevated temperatures. At 450K, the  $V_{TH}$  shifted by approximately 200 mV, and the drain current dropped by about 35%, resulting in a considerable increase in leakage current in the subthreshold region. The subthreshold slope for the MOSFET increased significantly with temperature, reaching around 160 mV/dec.

In comparison, under the same conditions, the SiC-JLT exhibited a slightly lower current of about 12 mA due to the absence of strong P-N junctions controlling the current flow. On the other hand, the SiC-JLT exhibited much better high-temperature performance. At 450K, the threshold voltage shift was only about 50 mV, and the drain current decreased by less than 15%. Importantly, in the subthreshold region, the SiC-JLT maintained lower leakage currents due to the better electrostatic control offered by the junctionless architecture. The SiC-JLT maintained a lower subthreshold slope of

Fig. 3.11: (a) Transfer characteristics  $V_{DS} = 1V$  and (b) output characteristics P<sup>+</sup>-SiCJLT at T = 300K to 600K at 50K step size for  $N_{P+} = 10^{18}$  cm<sup>-3</sup>,  $T_{P+} = 2$ nm at  $V_{GS} = 1V$  & compared with equivalent SiCJLT.

approximately 90 mV/dec at 450K, indicating better control over the subthreshold current. Combining JLT with SiC has better prospects for high-temperature applications [27, 28]. Such type of device has enormous potential in high voltage power MOS devices, system-on panels, and 3D stacked applications. Other authors have previously studied the breakdown voltages of such devices, which is one of the primary requirements of power electronics applications. For, example, Cheng et al found that polysilicon GAA JLFET gives a breakdown voltage (BV) of ~60 V due to the GAA structure, while the planar polysilicon FET shows poor breakdown performance [39]. However, it is well known that GAA transistors suffer from fabrication complexities.

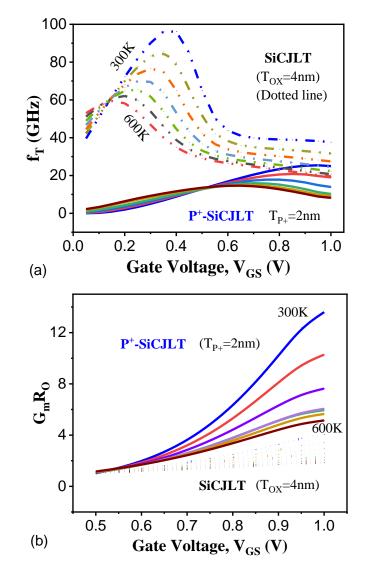

Fig. 3.12: (a)  $f_T$  with  $V_{GS}$  and (b) intrinsic gain with  $V_{GS}$  for P<sup>+</sup>-SiCJLT at T = 300K – 600K at 50K step sizem for  $N_{P+} = 10^{18}$  cm<sup>-3</sup>,  $T_{P+} = 2$ nm. This is compared with equivalent dimension SiCJLT.

Therefore, SiC JLTFET has been proposed to increase the breakdown voltage characteristics [27, 33]. Here in this paper, we propose a better transistor with much higher current performance and threshold voltage tunability.

GAA transistors require precise control over nanowire dimensions and multiple deposition steps for gate-all-around structures, which can be challenging and costly. In contrast, the P+-SiCJLT uses conventional planar processes with the addition of a P+ layer, which is simpler to integrate into existing fabrication lines. The P+-SiCJLT fabrication process avoids the need for advanced lithography and complex 3D structures, leading to lower overall production costs compared to GAA transistors.

## 3.8.2 Unity-gain Cut-Off Frequency at High Temperature

The unity-gain cut-off frequency,  $f_T (= G_m/2\pi(C_{GS} + C_{GD}))$  is one of the most important figures-of-merit for device applications in radio frequency applications. Where,  $C_{GS}$ ,  $C_{GD}$  are gate-to-source, and gate-to-drain capacitances respectively, including fringing and overlap capacitances. Small signal AC device simulation is executed at  $V_{DS} = 1V$  with an applied frequency of 1 MHz for the P<sup>+</sup>-SiCJLT with a P<sup>+</sup> layer thickness of 2nm.  $f_T$  is often influenced by geometrical parameters and parasitic capacitances. Minimum parasitic is desired for better  $f_T$  performance.

As shown in Fig. 3.12(a), there is a higher  $f_T$  for SiCJLT compared to P<sup>+</sup>-SiCJLT.  $f_T$  is degraded with an increase in T, for both the devices. Also, shown in Fig. 3.12(b) is the intrinsic gain (=  $G_m R_0$ ) of the P<sup>+</sup>-SiCJLT for T = 300 - 600K for  $N_{P+} = 10^{18}$  cm<sup>-3</sup> and  $T_{P+} = 2$ nm at a drain voltage of 1V.  $R_0$  is the output resistance. The intrinsic gain of a transistor is its maximum possible voltage gain, regardless of the bias point. Even though JLT has a slightly lesser  $G_m$  compared to a conventional MOS transistor, the intrinsic gain is better for a JLT as compared to its junction-based counterpart. P<sup>+</sup>-SiCJLT has better gain than SiCJLT both at room and high T, though for both the devices, gain decreases with an increase in T.

|                                  | V <sub>TH</sub> | Mode        | Temp | I <sub>ON</sub><br>/I <sub>OFF</sub> | $f_{\rm T}@V_{GS} = 1V$ | $G_{\rm m} R_{\rm O} @V_{GS} = 1V$ |

|----------------------------------|-----------------|-------------|------|--------------------------------------|-------------------------|------------------------------------|

|                                  |                 |             | 300K | 80                                   | 3.7×10 <sup>10</sup>    | 4.04                               |

| SiCJLT                           | -ve             | Depletion   | 400K | 58                                   | $2.7 \times 10^{10}$    | 2.93                               |

|                                  |                 |             | 500K | 40                                   | 2.2×10 <sup>10</sup>    | 2.28                               |

|                                  |                 |             | 300K | $7.0 \times 10^3$                    | 9.3×10 <sup>9</sup>     | 1.98                               |

| SD <sub>Pocket</sub> -<br>SiCJLT | +ve             | Enhancement | 400K | $0.5 \times 10^{3}$                  | 8.5×10 <sup>9</sup>     | 1.96                               |

| [28]                             |                 |             | 500K | $2.3 \times 10^2$                    | 7.9×10 <sup>9</sup>     | 1.90                               |

|                                  |                 |             | 300K | $8.0 \times 10^5$                    | $2.5 \times 10^{10}$    | 13.59                              |

| P <sup>+</sup> -<br>SiCJLT       | +ve             | Enhancement | 400K | 1.0×10 <sup>4</sup>                  | 1.3×10 <sup>10</sup>    | 7.62                               |

|                                  |                 |             | 500K | $0.9 \times 10^2$                    | 9.6×10 <sup>9</sup>     | 6.05                               |

**Table 3.1** Performance comparison of SiCJLT, sd<sub>pocket</sub>-sicjlt, P<sup>+</sup>-sicjlt

Fig. 3.13: Block diagram of SD<sub>Pocket</sub>-SiCJLT with P+ pocket thickness on 5nm.

# **3.9 Comparison with Devices Featuring Embedded Pockets in Substrate near Source/Drain Contact**

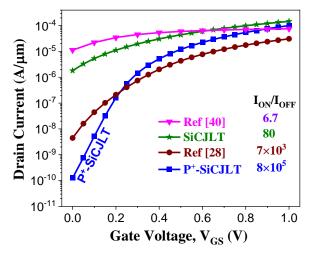

Finally, to see if the embedded P<sup>+</sup>pocket will have any advantages if placed on any other area, other than that in oxide, the device is compared with a device with embedded P<sup>+</sup> pockets of 5nm wide at source and drain sides (SD<sub>Pocket</sub>-SiCJLT), and P<sup>+</sup> doping of  $5 \times 10^{18} \text{ cm}^{-3}$  shown in Fig. 3.13 [28]. We use similar models and parameters as in the case of other JLTs. SD<sub>Pocket</sub>-SiCJLT is calibrated with [28]. Fig. 3.14 shows the comparison of  $I_{DS} - V_{GS}$  characteristics for SiCJLT, SD<sub>Pocket</sub>-SiCJLT, and P<sup>+</sup>-SiCJLT. As shown in Table 3.1, P<sup>+</sup>-SiCJLT outperforms the other devices considered in terms of  $I_{OFF}$ ,  $I_{ON}/I_{OFF}$  and enhancement mode operation, and intrinsic gain at room temperature. In addition, the  $V_{TH}$  tunability will also suffer in a device with P<sup>+</sup> pockets near the source/drain.

Therefore, P<sup>+</sup>-SiCJLT not only improves the  $I_{ON}/I_{OFF}$  ratio and scalability but also the efficacy of the transistor configuration for a power electronic switch.

Fig. 3.14:  $I_{ON}/I_{OFF}$  ratio comparison of P<sup>+</sup>-SiCJLT at  $N_{P+} = 10^{18} \text{ cm}^{-3}$ ,  $T_{P+} = 2 \text{ nm}$ , with equivalent SiCJLT ( $T_{OX} = 4 \text{ nm}$ ), and, SDPocket-SiCJLT (pocket width of 5 nm and  $T_{OX} = 4 \text{ nm}$ ).

As can be seen from Fig. 3.14, out of all the devices, namely P<sup>+</sup>-SiCJLT, SiCJLT, SD<sub>Pocket</sub>-SiCJLT [28] and embedding two P+ pockets in buried oxide [40]; SiCJLT and P<sup>+</sup>-SiCJLT has the similar order of ON-state currents at  $V_{GS} = 1V$ ; while P<sup>+</sup>-SiCJLT has better OFF-state current at  $V_{GS} = 0V$  by few orders of magnitude at room temperature. As these devices are to use in circuit simulations and eventually to some systems, evaluating circuit performance parameters at temperatures 300-500K are essential and are shown in Table 3.1. The devices are evaluated and compared in terms of switching capability  $(I_{ON}/I_{OFF}$  ratio), speed of operation (unity gain cut-off frequency,  $f_T$ ) and the maximum voltage gain of the transistor ( $G_m R_o$ ). The  $I_{ON}/I_{OFF}$  of P<sup>+</sup>-SiCJLT is 114 and 10<sup>4</sup> times higher than SD<sub>Pocket</sub>-SiCJLT and SiCJLT respectively at 300K. The value decreases with an increase in temperature for each device. SiCJLT, however has highest  $f_T$  followed by P<sup>+</sup>-SiCJLT (1.48 times higher) and SD<sub>Pocket</sub>-SiCJLT. As expected,  $f_T$  decreases, with an increase in temperature for all of the devices. P<sup>+</sup>-SiCJLT offer an intrinsic gain that is 6.9times higher than SD<sub>Pocket</sub>-SiCJLT and 3.4 times higher than SiCJLT at room temperature. Even at 500K, the intrinsic gain value of P<sup>+</sup>-SiCJLT is almost 3 times better than the other devices considered. Therefore, it can be concluded that P<sup>+</sup>-SiCJLT outperforms SD<sub>Pocket</sub>-SiCJLT and SiCJLT in terms of  $I_{ON}/I_{OFF}$  and  $G_m R_o$  as compared to other devices; even though  $f_T$ for P<sup>+</sup>-SiCJLT is only 1.48 times inferior to SiCJLT and better than SD<sub>Pocket</sub>-SiCJLT.

For high voltage or power electronics applications, a normally OFF MOSFET is favored for safe high-voltage operation and to alleviate OFF-state power dissipation. Depletion mode transistors require extra fail-safe circuitry in a power electronics circuit which leads to power dissipation [41, 42]. Enhancement mode transistors, on the other hand do not necessitate extra circuitry and therefore are power efficient and cost effective. To achieve an appreciable high current, a device needs to be highly doped, which however, results in a negative  $V_{TH}$ . There are significant efforts being made to convert a depletion mode transistor to enhancement mode one with including fundamental changes in structure designs at the cost of extra process steps and complexity, few examples are as follows. Chabak et al., fabricated an enhancementmode  $Ga_2O_3$  MOSFET empowered by arrays of Sn-doped non-planar fins on a semiinsulating (100)  $\beta - Ga_2O_3$  substrate to shift the  $V_{TH}$  from negative to positive value [42]. Because this is a non-planer kind of device, it needs additional fabrication steps to achieve enhancement mode operation and, therefore, is costly. Feng et al, realized the enhancement mode operation of a  $Ga_2O_3$  MOSFET by integrating a laminatedferroelectric (FE) charge storage gate (L-FeG) structure by replacing the normal gate dielectric material with an FE dielectric, which is again costly and may have reliability issues because of FE materials [43]. Naydenov et al, demonstrated that the junctionless FinFET with SiC material could be very attractive for lower voltage applications [44]. Therefore, in comparison to the existing methods for converting depletion to enhancement mode that needs extra process steps; our proposed structure achieves this enhancement mode operation just by inserting P+ pocket in relatively simple fabrication steps that is inexpensive and incredibly less time-consuming. This improvement in power dissipation becomes advantageous at higher temperatures and voltages. Therefore, the slight loss in current is compensated hugely by an immense gain in power loss.

## 3.10 Fabrication steps for the proposed device

The proposed structure can be fabricated in multiple ways. One of the possible fabrication workflows is described here.

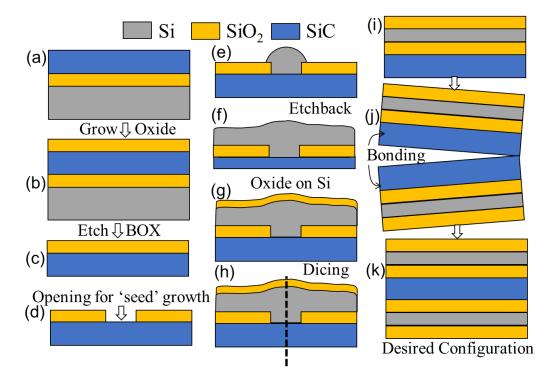

**Step 1:** Bonding: The fabrication process can start with a SiC wafer bonded to an SOI wafer, as in [17]. Another option is the hydrophobic wafer bonding process [45] (Fig. 3.15(a)).

Fig. 3.15: (a)-(k) Fabrication steps of a P<sup>+</sup>-SiCJLT.

**Step 2:** Growth of SiO2: The first SiO<sub>2</sub> layer can be deposited on the SiC substrate using wet oxidation in the presence of N<sub>2</sub>O and subsequent annealing in NO to reduce the impact of interface traps in SiC/SiO<sub>2</sub>, following the method proposed in Mudholkar et, al. [30] (Fig. 3.15(b)).

**Step 3:** Deposition of Si using 'Seed Growth' Method: Once the SiO<sub>2</sub> layer has been obtained, the Silicon layer (for embedded  $P^+$ ) can be grown using the 'seed method' employed in SOI wafers [46]. The growth of an epitaxial layer of silicon-on-insulator dioxide has been achieved previously, following the 'seed growth method' in several reports. In their paper, Kim et al. [47] achieved the growth of Silicon on SiO<sub>2</sub>. They also confirm a highly crystalline state by cross-sectional imaging and diffraction pattern analysis, surface roughness analysis, and wide-range epitaxy analysis. Researchers have also successfully co-integrated Logic Ultra-Thin Body and Box (UTBB) devices and bulk-Si I/O devices on the same chip, using a similar fabrication technique [48]. Not only Silicon, but deposition of epitaxial layers of materials like GaAs [49–51], and germanium [52, 53], on SiO<sub>2</sub> also has been reported using similar procedures (Fig. 3.15(c) –(f)).

**Step 4:** Growth of  $SiO_2$ :  $SiO_2$  can be further deposited on the newly grown Silicon using atomic layer deposition [54] or thermal oxidation [55] (Fig. 3.15(g)).

**Step 5:** Bonding to form double-gated structure: The fabricated wafers can then be diced and bonded using techniques such as hydrophobic wafer bonding process, to achieve the desired double gated structure [29, 54] (Fig. 3.15(h)- (k)).

### 3.11 Summary

We have proposed a new design of SiC junctionless transistors, by embedding  $P^+$  pockets in the oxides ( $P^+$ -SiCJLT).  $P^+$ -SiCJLT exhibits enhancement mode operation and offers excellent electrostatics which has enormous potential for application in high power electronics, memory, and IoT. The device offers multiple options for tuning the  $V_{TH}$  for different applications, by changing the  $P^+$  layer thickness,  $P^+$  layer doping, workfunction, and oxide thickness. This tremendously improves the device's scalability, as it is not limited by the fabrication constraint of a single dimension. We compared our device with an equidimensional traditional SiC JLT till high T. Although  $P^+$ -SiCJLT has a slightly lower On-current than an equivalent SiCJLT device, at the same applied bias, the improvement in  $I_{ON}/I_{OFF}$  makes up for it.  $P^+$ -SiCJLT offers better gain and inferior  $f_T$  than SiCJLT, making  $P^+$ -SiCJLT more fit for lower power and higher voltage

applications. The excellent characteristics of the  $P^+$ -SiCJLT are retained at a high temperature making it suitable for power electronics applications. With all these advantages, our device configuration takes a significant step forward toward the practicality of commercializing junctionless FETs.

## **Bibliography**

- [1] IEEE International roadmap for devices and systems (IRDS), https://irds.ieee.org/

- [2] Chenming Hu, Bokor, J., Tsu-Jae King, Anderson, E., Kuo, C., Asano, K., Takeuchi, H., Kedzierski, J., Wen-Chin, Lee. and Hisamoto, D. FinFET-a selfaligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices. 47, 2320–2325, 2000. https://doi.org/10.1109/16.887014

- [3] Colinge, J.-P. FinFETs and Other Multi-Gate Transistors. Springer US, Boston, MA, 2008.

- [4] Colinge, J.-P., Lee, C.-W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O'Neill, B., Blake, A., White, M., Kelleher, A.-M., McCarthy, B. and Murphy, R. Nanowire transistors without junctions. Nature Nanotech. 5, 225–229, 2010. https://doi.org/10.1038/nnano.2010.15

- [5] Lee, C.-W., Borne, A., Ferain, I., Afzalian, A., Yan, R., Dehdashti Akhavan, N., Razavi, P. and Colinge, J.-P. High-Temperature Performance of Silicon Junctionless MOSFETs. IEEE Transactions on Electron Devices. 57, 620–625, 2010. https://doi.org/10.1109/TED.2009.2039093

- [6] Baruah, R.K. and Paily, R.P. A Dual-Material Gate Junctionless Transistor With High- k Spacer for Enhanced Analog Performance. IEEE Transactions on Electron Devices. 61, 123–128, 2014. https://doi.org/10.1109/TED.2013.2292852

- [7] Kumar, M.J. and Sahay, S. Controlling BTBT-Induced Parasitic BJT Action in Junctionless FETs Using a Hybrid Channel. IEEE Transactions on Electron Devices. 63, 3350–3353, 2016. https://doi.org/10.1109/TED.2016.2577050

- [8] Baliga, B.J. Power semiconductor device figure of merit for high-frequency applications. IEEE Electron Device Letters. 10, 455–457, 1989. https://doi.org/10.1109/55.43098

- [9] Johnson, E. Physical limitations on frequency and power parameters of transistors. In: IRE International Convention Record. pp. 27–34. Institute of Electrical and Electronics Engineers, New York, NY, USA, 1965.

- [10] Bolokian, M., Orouji, A.A., Abbasi, A. and Noribayat, R. Complete depletion area in SOI junctionless FETs by multiple buried P-type pockets. Eur. Phys. J. Plus. 138, 527, 2023. https://doi.org/10.1140/epjp/s13360-023-04147-2

- [11] Sahay, S. and Kumar, M.J. Junctionless Field-Effect Transistors: Design, Modeling, and Simulation. Wiley, 2019.

- [12] Park, C.-H., Ko, M.-D., Kim, K.-H., Sohn, C.-W., Baek, C.K., Jeong, Y.-H. and Lee, J.-S. Comparative study of fabricated junctionless and inversion-mode nanowire FETs. In: 69th Device Research Conference. pp. 179–180, 2011.

- [13] Choi, S.-J., Moon, D.-I., Kim, S., Duarte, J.P. and Choi, Y.-K. Sensitivity of

Threshold Voltage to Nanowire Width Variation in Junctionless Transistors. IEEEElectronDeviceLetters.32,125–127,2011.https://doi.org/10.1109/LED.2010.2093506

- [14] Fan, J., Li, M., Xu, X., Yang, Y., Xuan, H., and Huang, R. Insight Into Gate-Induced Drain Leakage in Silicon Nanowire Transistors. IEEE Transactions on Electron Devices. 62, 213–219, 2015. https://doi.org/10.1109/TED.2014.2371916

- [15] Shenai, K. The Figure of Merit of a Semiconductor Power Electronics Switch. IEEE Transactions on Electron Devices. 65, 4216–4224, 2018. https://doi.org/10.1109/TED.2018.2866360

- [16] Keyes, R.W. Figure of merit for semiconductors for high-speed switches. Proceedings of the IEEE. 60, 225–225, 1972. https://doi.org/10.1109/PROC.1972.8593

- [17] Pérez-Tomás, A., Lodzinski, M., Guy, O.J., Jennings, M.R., Placidi, M., Llobet, J., Gammon, P.M., Davis, M.C., Covington, J.A., Burrows, S.E. and Mawby, P.A. Si/SiC bonded wafer: A route to carbon free SiO2 on SiC. Applied Physics Letters. 94, 103510, 2009. https://doi.org/10.1063/1.3099018

- [18] Casady, J.B. and Johnson, R.W. Status of silicon carbide (SiC) as a wide-bandgap semiconductor for high-temperature applications: A review. Solid-State Electronics. 39, 1409–1422, 1996. https://doi.org/10.1016/0038-1101(96)00045-7

- [19] Madadi, D. and Orouji, A.A. Investigation of tied double gate 4H–SiC junctionless FET in 7 nm channel length with a symmetrical dual p+ layer. Physica E: Lowdimensional Systems and Nanostructures. 126, 114450, 2021. https://doi.org/10.1016/j.physe.2020.114450

- [20] Wang, B., Huang, W., Chi, L., Al-Hashimi, M., Marks, T.J. and Facchetti, A. High-k Gate Dielectrics for Emerging Flexible and Stretchable Electronics. Chem. Rev. 118, 5690–5754, 2018. https://doi.org/10.1021/acs.chemrev.8b00045

- [21] Paz, B.C., Ávila-Herrera, F., Cerdeira, A. and Pavanello, M.A. Double-gate junctionless transistor model including short-channel effects. Semicond. Sci. Technol. 30, 055011, 2015. https://doi.org/10.1088/0268-1242/30/5/055011

- [22] Willander, M., Friesel, M., Wahab, Q. and Straumal, B. Silicon carbide and diamond for high temperature device applications. Journal of Materials Science Materials in Electronics. 17, 1, 2006.

- [23] Mahajan, B.K., Chen, Y.-P., Noh, J., Ye, P.D. and Alam, M.A. Electrothermal performance limit of β-Ga2O3 field-effect transistors. Applied Physics Letters. 115, 173508, 2019. https://doi.org/10.1063/1.5116828

- [24] Mahajan, B.K., Chen, Y.-P., Zagni, N. and Alam, M.A. Self-Heating and Reliability-Aware "Intrinsic" Safe Operating Area of Wide Bandgap Semiconductors—An Analytical Approach. IEEE Transactions on Device and Materials Reliability. 21, 518–527, 2021. https://doi.org/10.1109/TDMR.2021.3112389

- [25] Peng, X., Hu, X., Wang, W. and Song, L. Mechanical Properties of Silicon Carbonitride Thin Films. Japanese Journal of Applied Physics. 42, 620–622, 2003. https://doi.org/10.1143/JJAP.42.620

- [26] Wang, Z., Shi, X., Tolbert, L.M., Wang, F., Liang, Z., Costinett, D. and Blalock,

B.J. A high temperature silicon carbide mosfet power module with integrated silicon-on-insulator-based gate drive. IEEE Transactions on Power Electronics. 30, 1432–1445, 2015. https://doi.org/10.1109/TPEL.2014.2321174

- [27] Singh, J. and Kumar, M.J. A Planar Junctionless FET Using SiC With Reduced Impact of Interface Traps: Proposal and Analysis. IEEE Transactions on Electron Devices. 64, 4430–4434, 2017. https://doi.org/10.1109/TED.2017.2752227

- [28] Singh, J., Jain, A.K. and Kumar, M.J. Realizing a Planar 4H-SiC Junctionless FET for Sub-10-nm Regime Using P+ Pocket. IEEE Transactions on Electron Devices. 66, 3209–3214, 2019. https://doi.org/10.1109/TED.2019.2914633

- [29] Madadi, D. and Orouji, A. β-Ga2O3 double gate junctionless FET with an efficient volume depletion region. Physics Letters A. 412, 127575, 2021. https://doi.org/10.1016/j.physleta.2021.127575

- [30] McNutt, T., Hefner, A., Mantooth, A., Berning, D. and Sei-Hyung, R. Silicon Carbide Power MOSFET Model and Parameter Extraction Sequence." IEEE 34th Annual Conference on Power Electronics Specialist, 2003. https://doi.org/10.1109/pesc.2003.1218298.

- [31] Mudholkar, M. and Mantooth, H.A. Characterization and Modeling of 4H-SiC Lateral MOSFETs for Integrated Circuit Design. IEEE Transactions on Electron Devices. 60, 1923–1930, 2013. https://doi.org/10.1109/TED.2013.2258287

- [32] Sentaurus Device User: Sentaurus TCAD Version R-2020.09-SP1

- [33] Baruah, R.K., Mahajan, B.K., Chen, Y.-P. and Paily, R.P. A Junctionless Silicon Carbide Transistor for Harsh Environment Applications. J. Electron. Mater. 50, 5682–5690, 2021. https://doi.org/10.1007/s11664-021-09087-0

- [34] Gundapaneni, S., Ganguly, S. and Kottantharayil, A. Bulk Planar Junctionless Transistor (BPJLT): An Attractive Device Alternative for Scaling. IEEE Electron Device Letters. 32, 261–263, 2011. https://doi.org/10.1109/LED.2010.2099204

- [35] Aminzadeh, P., Alavi, M. and Scharfetter, D. Temperature dependence of substrate current and hot carrier-induced degradation at low drain bias. In: Symposium on VLSI Technology Digest of Technical Papers (Cat. No.98CH36216). pp. 178–179. IEEE, Honolulu, HI, USA, 1998.

- [36] Jeon, D.S. and Burk, D.E. MOSFET electron inversion layer mobilities-a physically based semi-empirical model for a wide temperature range. IEEE Transactions on Electron Devices. 36, 1456–1463, 1989. https://doi.org/10.1109/16.30959

- [37] Doria Trevisoli, R., Trevisoli Doria, R., de Souza, M., Das, S., Ferain, I. and Antonio Pavanello, M. The zero temperature coefficient in junctionless nanowire transistors. Applied Physics Letters. 101, 062101, 2012. https://doi.org/10.1063/1.4744965

- [38] Baruah, R.K. and Paily, R.P. High-temperature effects on device performance of a junctionless transistor. In: 2012 International Conference on Emerging Electronics. pp. 1–4, 2012.

- [39] Cheng, Y.-C., Wu, Y.-C., Chen, H.-B., Han, M.-H., Lu, N.-H., Su, J.-J. and Chang, C.-Y. High voltage characteristics of junctionless poly-silicon thin film transistors. Applied Physics Letters. 103, 123510, 2013. https://doi.org/10.1063/1.4821856

- [40] Aghaeipour, Z. and Naderi, A. Embedding Two P+ Pockets in the Buried Oxide of Nano Silicon on Insulator MOSFETs: Controlled Short Channel Effects and Electric Field. Silicon. 12, 2611–2618, 2020. https://doi.org/10.1007/s12633-019-00358-4

- [41] Wong, H.Y., Braga, N., Mickevicius, R.V. and Ding, F. Normally-OFF dual-gate Ga2O3 planar MOSFET and FinFET with high ION and BV. In: 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD). pp. 379–382. IEEE, Chicago, IL, 2018.

- [42] Chabak, K.D., Moser, N., Green, A.J., Walker, D.E., Jr., Tetlak, S.E., Heller, E., Crespo, A., Fitch, R., McCandless, J.P., Leedy, K., Baldini, M., Wagner, G., Galazka, Z., Li, X. and Jessen, G. Enhancement-mode Ga2O3 wrap-gate fin fieldeffect transistors on native (100) β-Ga2O3 substrate with high breakdown voltage. Applied Physics Letters. 109, 213501, 2016. https://doi.org/10.1063/1.4967931

- [43] Feng, Z., Cai, Y., Li, Z., Hu, Z., Zhang, Y., Lu, X., Kang, X., Ning, J., Zhang, C., Feng, Q., Zhang, J., Zhou, H. and Hao, Y. Design and fabrication of field-plated normally off β-Ga2O3 MOSFET with laminated-ferroelectric charge storage gate for high power application. Applied Physics Letters. 116, 243503, 2020. https://doi.org/10.1063/5.0010561

- [44] Naydenov, K., Donato, N. and Udrea, F. Operation and performance of the 4H-SiC junctionless FinFET. Eng. Res. Express. 3, 035008, 2021. https://doi.org/10.1088/2631-8695/ac12bc

- [45] Gammon, P.M., Chan, C.W., Li, F., Gity, F., Trajkovic, T., Pathirana, V., Flandre, D. and Kilchytska, V. Development, characterisation and simulation of wafer bonded Si-on-SiC substrates. Materials Science in Semiconductor Processing. 78, 69–74, 2018. https://doi.org/10.1016/j.mssp.2017.10.020

- [46] Nakamura, T. Method for forming SOI structure, https://patents.google.com/patent/US5417180A/en, 1995.

- [47] Kim, S.-H., Lee, S.H., Park, J.-W., Roh, T.M. and Suh, D. *In situ* implementation of silicon epitaxial layer on amorphous SiO2 using reduced-pressure chemical vapor deposition. Applied Materials Today. 24, 101143, 2021. https://doi.org/10.1016/j.apmt.2021.101143

- [48] Huguenin, J.-L., Monfray, S., Denorme, S., Bidal, G., Perreau, P., Barnola, S., Samson, M.-P., Benotmane, K., Loubet, N., Campidelli, Y., Leverd, F., Abbate, F., Clement, L., Borowiak, C., Golanski, D., Fenouillet-Beranger, C., Boeuf, F., Ghibaudo, G. and Skotnicki, T. Localized SOI logic and bulk I/O devices cointegration for Low power System-on-Chip technology. In: Proceedings of 2010 International Symposium on VLSI Technology, System and Application. pp. 118– 119. IEEE, Hsin Chu, Taiwan, 2010.

- [49] Coste, M., Molière, T., Cherkashin, N., Hallais, G., Vincent, L., Bouchier, D. and Renard, C. Morphology of GaAs crystals heterogeneously integrated on nominal (001) Si by epitaxial lateral overgrowth on tunnel oxide via Ge nano-seeding. Thin Solid Films. 647, 13–18, 2018. https://doi.org/10.1016/j.tsf.2017.12.015

- [50] Renard, C., Cherkashin, N., Jaffre, A., Molière, T., Hallais, G., Vincent, L., Alvarez, J., Mencaraglia, D., Michel, A. and Bouchier, D. Growth of high quality micrometer scale GaAs/Si crystals from (001) Si nano-areas in SiO2. Journal of Crystal Growth. 401, 554–558, 2014.

https://doi.org/10.1016/j.jcrysgro.2014.01.065

- [51] Li, J.Z., Bai, J., Park, J.-S., Adekore, B., Fox, K., Carroll, M., Lochtefeld, A. and Shellenbarger, Z. Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping. Applied Physics Letters. 91, 021114, 2007. https://doi.org/10.1063/1.2756165

- [52] Park, J.-S., Bai, J., Curtin, M., Adekore, B., Carroll, M. and Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90, 052113, 2007. https://doi.org/10.1063/1.2435603

- [53] Nam, J.H., Alkis, S., Nam, D., Afshinmanesh, F., Shim, J., Park, J.-H., Brongersma, M., Okyay, A.K., Kamins, T.I. and Saraswat, K. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416, 21–27, 2015. https://doi.org/10.1016/j.jcrysgro.2014.11.004

- [54] Zheng, H., Mahajan, B.K., Su, S.C., Mukherjee, S., Gangopadhyay, K. and Gangopadhyay, S. Barrier Modification of Metal-contact on Silicon by Sub-2 nm Platinum Nanoparticles and Thin Dielectrics. Sci Rep. 6, 25234, 2016. https://doi.org/10.1038/srep25234

- [55] Moslehi, M.M., Shatas, S.C. and Saraswat, K.C. Thin SiO2 insulators grown by rapid thermal oxidation of silicon. Applied Physics Letters. 47, 1353–1355, 1985. https://doi.org/10.1063/1.96278