# **CHAPTER 5**

### Fabrication and Characterization of WS2-FET

#### **Contents:**

- 5.1. Introduction

- 5.2. Experiment

- 5.2.1. WS<sub>2</sub>-FET Fabrication

- 5.2.2. Electrical Characterization of WS<sub>2</sub>-FET

- 5.3. Results and Discussion

- 5.3.1. Spectroscopic Analysis of WS<sub>2</sub> Film Before and After Fabrication

- 5.3.2. Electrical Characterization of WS<sub>2</sub>-FET

- 5.3.3. Channel length Variation of the WS<sub>2</sub> -FET

- 5.3.4. Doping Effect in WS<sub>2</sub> FET

- 5.3.5. Measurement of Threshold Voltage and Intrinsic Mobility Using Y-function Method

- 5.3.6. Measurement of Contact Resistance at the Metal-WS<sub>2</sub> Interface

- 5.4. Summary

Bibliography

#### 5.1. Introduction:

The semiconducting nature of WS<sub>2</sub> nanosheets has sparked considerable interest in FET applications due to its unique properties and compatibility with atomically thin device architectures [1-4]. WS<sub>2</sub> nanosheets, with a tunable bandgap larger than that of traditional silicon-based semiconductors, make a compelling case for next-generation FETs [5, 6]. This tunable bandgap can be engineered according to application needs, providing versatility in device performance [7-10]. However, WS2-based FETs face challenges related to stability, as environmental effects degrade the intrinsic properties of WS<sub>2</sub> over time. This degradation negatively impacts the performance of WS<sub>2</sub> as a channel material, leading to reduced operating efficiency and reliability of WS2-based FETs in practical applications [11, 12]. Numerous studies have shown that the mobility of CVDgrown WS<sub>2</sub> devices, ranging from 5.8 to 33 cm<sup>2</sup>/V.s, is significantly lower than the theoretically predicted values. This discrepancy is primarily attributed to factors such as interfacial charged impurities, surface traps, roughness of the underlying dielectric layer, atomic defects or vacancy etc. [13]. The interfacial characteristics, along with the inherent dielectric properties of the insulating layer, present significant challenges in device fabrication and electrical transport [15,16]. Furthermore, the process of transferring WS<sub>2</sub> flakes onto target substrates has a significant impact on the quality and performance of the device [16, 17]. For the fabrication of WS<sub>2</sub>-based FETs, both liquid and dry transfer techniques are widely used, each of which offer distinct challenges in the transfer process, with results to the maintenance of nanosheets structural integrity and minimizing contamination [7,19,20]. The dry technique stands out among the two due to its simple transfer process, cost-effectiveness and high yield. However, it is often time-consuming which require careful handling to ensure precision and maintain the pristine properties of the material. Optimizing these transfer methods is crucial to ensure transfer stability and achieve superior electrical performance of fabricated devices.

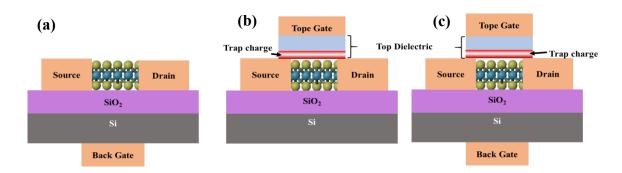

The structures of 2D material-based FETs can be categorized into three types: back-gated, top-gated, and dual-gated, as depicted in Fig. 5.1. Each of these device structures presents specific challenges and applications. Illarionov et al. have highlighted that achieving a damage-free transfer of the oxide layer onto 2D materials remains a significant challenge [20]. This difficulty is particularly critical as it exacerbates the stability issues in 2D material-based electronic devices. These stability limitations

primarily arise from charge trapping caused by defects in the oxide layer, located near the channel/oxide interface. Choi et al. reported that when Al<sub>2</sub>O<sub>3</sub> is used as a top gate on an MoS<sub>2</sub> surface, shallow and deep-level traps are present at or near the ALD-grown Al<sub>2</sub>O<sub>3</sub> [21]. The existence of charge traps can result in transfer curve hysteresis of FET, which are often found at the interface between the semiconductor channel and the dielectric layer. The presence of traps can arise from various factors, including surface defects, impurities, or defects in the dielectric material. When the gate voltage is applied, charge carriers can become trapped at the dielectric-channel interface of FET, causing a delay in the device's response, as shown in Fig 5.1( a & b). As the gate voltage is swept back, the trapped charges are gradually released, leading to a shift in the transfer curve and resulting in hysteresis [22]. This hysteresis can significantly impact FET performance, causing instability in switching behaviour and affecting the device's reliability. Additionally, hysteresis can lower the on/off current ratio, degrade the threshold voltage, and increase power consumption due to energy loss from the charging and discharging of traps. Furthermore, hysteresis can cause inconsistencies in the current-voltage characteristics, making it difficult to control the FET's switching operation with precision.

**Fig. 5.1**: Illustrative representation of the various 2D-FET structures. (a) Back-gate FET, where the gate electrode is located beneath the dielectric layer and the channel material. (b) Top-gate FET, where the gate electrode is positioned on top of the channel material with an insulating layer separating them (c) Dual-gated FET, which incorporates both top and back gates

A dual-gated FET features a sophisticated device architecture that incorporates two gate electrodes: a top gate positioned on the surface of the nanosheet and a back gate located on the backside of the device [23]. This configuration provides improved electrostatic control over the channel, enhancing the device's overall performance and

functionality. However, it shares similar limitations with top-gated FETs. Additionally, for MX<sub>2</sub> materials, challenges such as the absence of chemical bonds at the 2D surface, difficulties in dielectric deposition, and the scaling of the Equivalent Oxide Thickness (EOT) remain significant obstacles [24].

In this chapter, the fabrication and characterization of back-gated FL-WS<sub>2</sub>-FET is presented. The devices were fabricated using Si/SiO<sub>2</sub> substrate where SiO<sub>2</sub> acts as the back-gate dielectric. The SiO<sub>2</sub>/Si substrate is commercially available and it reduces fabrication complexity by eliminating the need for the deposition of gate dielectric. The back gate design is ideal for academic research of TMD-based FETs as it allows consistent gate control, facilitating the study of 2D materials such as WS<sub>2</sub> material which acts as a channel material [25,26]. The back-gated structure in 2D material-based FETs facilitates effective electrostatic manipulation of the channel, allowing for efficient modulation of charge carriers [17]. This leads to a higher current on/off ratio, reduced leakage current, and improved performance by minimizing interface traps [25]. As a result, the device experiences enhanced carrier mobility and greater stability, contributing to overall improved functionality and reliability. Furthermore, this design enables the investigation of device performance with limited intricacy in manufacturing, making it a perfect setting for initial material analysis and proof-of-concept research. The back-gated FET structure is well-suited for initial studies and characterization of 2D material-based FETs, providing a simple and efficient platform for evaluating device performance. However, its scalability and adaptability for more complex electronic systems present challenges that must be addressed when transitioning to more advanced device architecture [9,23]. Despite these limitations, back-gated FETs remain a reliable choice for WS<sub>2</sub>-based research, offering a solution for the preliminary evaluation of device performance in the early stages of development [28].

To understand the influence of fabrication parameters, variations in device performance were systematically analyzed by employing different metal contacts and adjusting the channel lengths. To achieve a micron-scale channel, the source and drain contact regions were meticulously patterned using mask-less lithography, ensuring precise alignment and enhanced device reproducibility. Spectroscopic methods were employed to study and optimize the device structure, position of WS<sub>2</sub> nanosheet, etc. both pre and post-fabrication, ensuring robust stability and high-quality interfaces. The electrical transport characteristics of the fabricated WS<sub>2</sub>-FET offer detailed insights into

the device's performance. Key parameters such as field-effect mobility, on/off current ratio, and subthreshold swing were derived from I-V measurements performed with a parameter analyzer. These findings demonstrate the promising potential of WS<sub>2</sub>-based FETs in advanced semiconductor technology applications. The challenges in the fabrication process are also highlighted. Furthermore, the use of different metal contacts, variations in channel length and doping levels offer critical insights into the M-S interface, carrier concentration, mobility, and overall performance of the FETs.

#### **5.2.** Experiment:

#### 5.2.1. WS<sub>2</sub>-FET Fabrication:

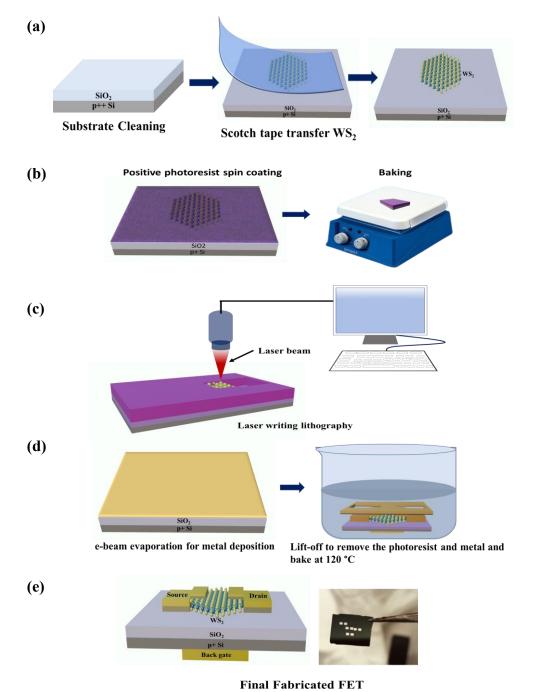

Fig. 5.2 represents the fabrication process steps of the back-gated WS<sub>2</sub> FET began on a Si substrate coated with 300 nm SiO<sub>2</sub>, which served as the back-gate dielectric. Prior to transferring the nanosheet, one side of the SiO<sub>2</sub> layer on the Si substrate was etched using Hydrofluoric Acid (HF), then rinsed with DI water and dried using a Nitrogen (N<sub>2</sub>) flow. Then the HF-treated SiO<sub>2</sub>-coated Si substrate was thoroughly cleaned with ACE, IPA, and DI water for 15 minutes each in a bath sonication and then dried with a flow of N<sub>2</sub> to eliminate any remaining impurities or particles from the substrate.

To make a WS<sub>2</sub> channel for FET, the WS<sub>2</sub> flake was transferred onto the SiO<sub>2</sub> substrate using a dry transfer method with scotch tape, as shown in Fig 5.2(a). Initially, a few-layer WS<sub>2</sub> nanosheet was obtained via liquid-phase exfoliation from bulk WS<sub>2</sub> powder then the exfoliated nanosheets were deposited onto the Si substrate and dried at 60 °C for an hour. The exfoliation process of a few-layer WS<sub>2</sub> flake is comprehensively discussed in Chapter 3. Then the exfoliated nanosheets were transferred using scotch tape onto the SiO<sub>2</sub> surface, eliminating the need for additional chemicals or high-temperature process.

Fig. 5.2(b-d) represents the photolithography process used as the patterning technique to define the source-drain contacts and the channel area. Prior to the lithography process, a positive photoresist was applied to the WS<sub>2</sub>-coated SiO<sub>2</sub> substrate through spin-coating at 2000 rpm for 60 seconds. The coated substrate was then baked at 120 °C for 5 minutes to ensure proper adhesion and uniformity of the photoresist layer. The photolithography process was carried out using a high-resolution laser lithography system (Dilase 250, 50× magnification), featuring a 1 μm laser spot size and a writing speed of over 100 mm/s. The system is equipped with an inbuilt camera that enables precise

identification of particles on the substrate, facilitating accurate patterning of the selected region. In this process, a design was created using K-layout software to define the specified contact area at precise locations on the substrate. During the WS<sub>2</sub>-FET fabrication, the prepared pattern was transferred onto a single WS<sub>2</sub> flake using a precise line-by-line laser writing technique as depicted in Fig. 5.2(c).

Fig. 5.2: Schematic depiction of the sequential steps of the device fabrication using contactless photography process

However, creating a microchannel of a few microns on a small nanosheet (<10  $\mu m$ ) is extremely challenges due to potential pattern overlaps. Conventional photolithography poses challenges in fabricating channel lengths below ~8-10  $\mu m$ . Achieving patterns in areas smaller than 10  $\mu m$  is particularly difficult, as it requires precise alignment of the lithography mask on the substrate. To address these limitations, the fabrication of the FET was carried out using a two-step lithography process using laser writing photolithography. This approach ensures greater precision in patterning and allows for the realization of micron-scale spacing between contacts on the WS2 surface. A channel area of 2-4  $\mu m$  x 5  $\mu m$  is successfully patterned without requiring external masks using two-step laser writing photolithography. This method offers an alternative approach for fabricating 2D-FET devices by overcoming the challenges of contact lithography, particularly the difficulty of accurately aligning patterned masks on nanosheets smaller than 10  $\mu m$ .

First, the pattern for one side contact area was exposed to the laser, with the corresponding pattern file applied to a specific region of the  $WS_2$  nanosheet. After defining one side of the contact area, the laser-exposed substrate was developed in a photoresist developer solution for  $\sim 30$  seconds to dissolve the illuminated region. It was then rinsed with DI water, dried with a  $N_2$  flow and baked at 120 °C for 5 minutes to remove any remaining residues from the exposed area.

The Metal electrodes of Cr/Ag and Ti/Ag( $\sim$ 5/70 nm thick) were deposited using e-beam evaporation. Excess metal and photoresist were removed through a lift-off process, which involved soaking the substrate in acetone at room temperature for 10-15 minutes, as shown in Fig. 5.2(d). To eliminate any remaining metal particles, a gentle flow of  $N_2$  was used to wash away the impurities.

After successfully preparing the metal contact on one side of the WS<sub>2</sub> flake, the opposite side of the contact area was patterned using the same process. This process involved applying a layer of photoresist, followed by metal deposition, and finally, a lift-off technique. However, precise control over the contact area is crucial due to the small size of the flake and the micron-scale spacing required between the contacts. Lastly the back side of the metal contact Aluminium (Al) which acts as a gate contact was deposited through thermal evaporation. The final device structure is depicted in Fig. 5.2(e).

High-resolution optical microscopy was employed to obtain clear images of the device structure to verify the morphology and correct placement of metal contacts on the

nanosheet surface. Additionally, the fabricated FET nanosheets were first analyzed using Raman spectroscopy with a 532 nm laser source (Raman Model: CPX100) and further the structural morphology of the nanosheets were examined using AFM and FESEM.

#### **5.2.2.** Electrical Characterization of WS<sub>2</sub>-FET:

The structural and morphological properties of the fabricated FET were analyzed using spectroscopic techniques, while the electrical characteristics of the back-gated WS2 channel-based FET device were evaluated by applying a DC voltage. Measurements were performed in a dark chamber at room temperature.

#### 5.3. Results and Discussion:

# **5.3.1.** Spectroscopic Analysis of WS<sub>2</sub> Film Before and After Fabrication:

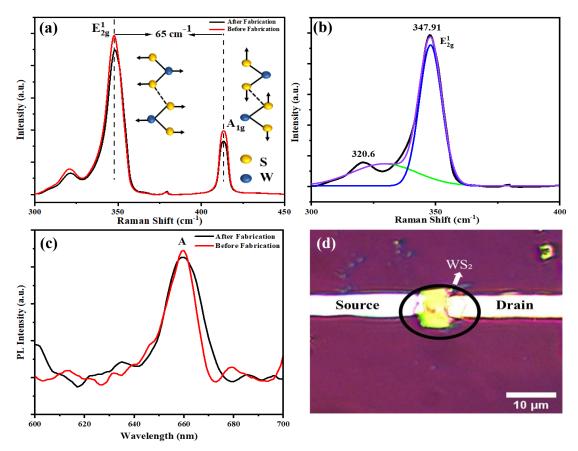

Raman spectroscopy is a premier high-resolution technique essential for the detailed study of the fundamental properties and structural characteristics of 2D materials. The Raman spectra were measured using a 532 nm laser, and displayed two vibrational peaks between 300-500 cm<sup>-1</sup> which appear on the x-axis of the Raman spectra, corresponding to the  $A_{1g}$  and  $E_{2g}^1$  modes as shown in Fig. 5.3(a). The Raman spectra were meticulously recorded before and after the fabrication processes. The intensity difference between the  $A_{1g}$  and  $E_{2g}^1$  peaks is ~65 cm<sup>-1</sup>, indicating a few-layer nanosheets [29–31]. In addition, a second-order longitudinal acoustic 2LA(M) mode is identified at 347.91 cm<sup>-1</sup> for pre and post-lithography processed samples. Although this 2LA(M) mode overlaps with the first-order  $E_{2g}^1$  mode, the application of multi-peak Lorentzian fitting techniques allows for the precise determination of peak positions within the spectra, as depicted in Fig. 5.3(b). Interestingly, while the lithography process does not alter the positions of the peaks, there is a slight decrease in intensity, which is likely attributed to impurities introduced during the fabrication process.

The optical characteristics of the exfoliated WS<sub>2</sub> nanosheets after device fabrication were thoroughly investigated using PL measurements conducted on the same instrument with an excitation wavelength of 532 nm at room temperature. As shown in Fig. 5.3(c), a prominent emission peak corresponding to the A-exciton was observed for the WS<sub>2</sub> nanosheets [32]. It is noteworthy that the position of this peak remained constant

despite variations in the excitation wavelength, although the peak's intensity either decreased or dispersed. A distinct sharp peak observed near 1.8 eV (equivalent to 655 nm) corresponds to the indirect band gap emission, signifying the presence of few-layer WS<sub>2</sub>. Fig. 5.3(d) shows the examination of the WS<sub>2</sub>-FET structure after fabrication, where an optical microscope was used to inspect the contact area and verify the correct placement on the nanosheet surface.

**Fig. 5.3:** (a) Raman Spectroscopy of the FL-WS<sub>2</sub> nanosheet before and after lithography-based fabrication (b) spectral fitting with Lorentzian curves for 2LM and E<sup>1</sup><sub>2g</sub> and (c) PL Spectroscopy of the exfoliated WS<sub>2</sub> nanosheets and (d) Optical microscopic image of the photolithography patterned FL-WS<sub>2</sub> FET device

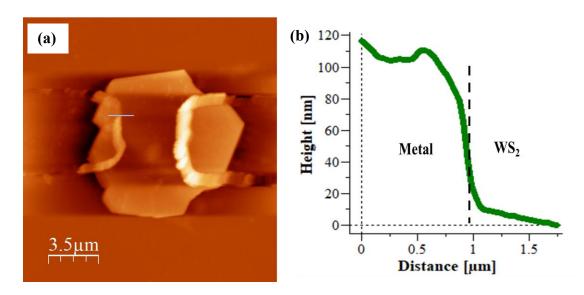

AFM measurement was conducted for the fabricated device using tapping mode under ambient conditions, as shown in Fig. 5.4. The detailed analysis of the surface roughness of WS<sub>2</sub> was made. The AFM images reveal that the WS<sub>2</sub> surface exhibits significant roughness, likely due to the presence of impurities or residues of photoresist during the fabrication process. The measured average thickness of the WS<sub>2</sub> layers was found to be less than 10 nm, suggesting that the thin WS<sub>2</sub> flakes consist of only a few

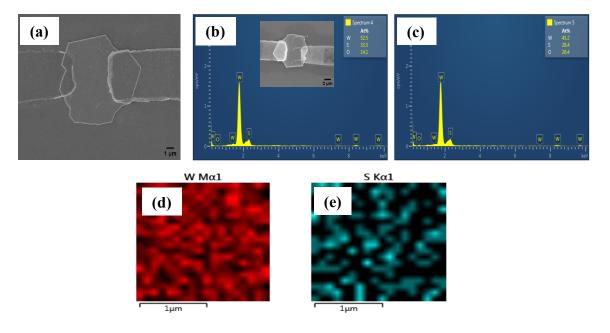

layers. Fig. 5.5(a) shows the FESEM image of the WS<sub>2</sub> device show that the metal electrode was is align perfectly with the same WS<sub>2</sub> flake. The precise alignment and spacing are very important for proper electrical contact with the metal electrode to function the device efficiently.

**Fig. 5.4:** (a) AFM image of the Fabricated FL-WS<sub>2</sub> device with <10 nm thick nanosheet and (b) corresponding height profiling of the Metal and WS<sub>2</sub> after the fabrication of the FET

**Fig. 5.5:**(a) FESEM image of the Fabricated FL-WS<sub>2</sub> device, (b & c) EDX spectra of the FL-WS<sub>2</sub> flake captured from different regions of the nanosheet and (d-e) corresponding colour mapping of the W and S atoms in the WS<sub>2</sub> flake.

Fig. 5.5(b-e) shows the EDX analysis of WS<sub>2</sub> after the fabrication of the FET. The elemental mapping of WS<sub>2</sub> provides an intuitive visualization of the distribution of W and S elements across the examined region. These distributions were quantified in terms of their atomic percentages, as shown in the EDX spectra. The analysis revealed that the atomic percentage of S atom (~33% and ~28%) indicated in the Fig. 5.5 (b & c) which is significantly lower than that of W atom (~52% and ~55%). This discrepancy could be attributed to vacancies created in the atomic lattice during the exfoliation process [2]. However, the presence of O atoms in the WS<sub>2</sub> nanosheet is attributed to their ability to occupy the vacant sites of S atoms. Due to the presence of S vacancies in the WS<sub>2</sub> lattice, O atoms occupy these vacant positions during the exfoliation and device fabrication processes. In the previous chapter, we discussed that the presence of O atoms and S vacancies within the atomic lattice of WS<sub>2</sub> can lead to a reduction in the bandgap of WS<sub>2</sub>. Moreover, the observed lower S atomic ratio and the presence of O atoms imply that S vacancies in WS<sub>2</sub> could significantly impact the electrical properties of WS<sub>2</sub>-based FET devices. These vacancies could alter charge transport and influence device performance.

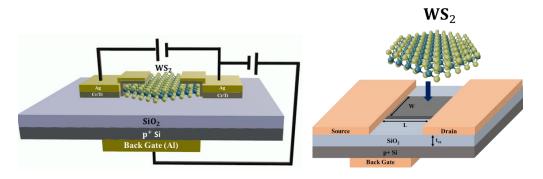

Fig. 5.6: Schematic depiction of the back gated WS<sub>2</sub>-FET structure on SiO<sub>2</sub>/Si substrate

#### **5.3.2.** Electrical Characterization of WS<sub>2</sub>-FET:

To examine the operating performance of the fabricated WS<sub>2</sub>-FET, the electrical measurement was performed using a Keithley SCS 4200 semiconductor parameter analyzer at room temperature. Key electrical properties such as contact type (ohmic or Schottky),  $R_C$ ,  $V_{th}$ ,  $\mu_{FE}$ , etc of back-gated WS<sub>2</sub>-FET were analyzed. The device structure and bias configuration to studying characteristics of FET is shown in Fig. 5.6. The output characteristics of the WS<sub>2</sub>-FET, where drain current ( $I_{ds}$ ) is plotted as a function of Drain-Source Voltages ( $V_{ds}$ ) at a constant Gate-Source Voltage ( $V_{gs}$ ). Ag is used as the metal contact. Two different metals Ti and Cr were used as adhesion layers for the FET

fabrication. Two FETs were fabricated on separate flakes, each with a thickness of less than  $\sim \! 10$  nm. The FETs' L is approximately 2  $\mu$ m, while the W is about 5  $\mu$ m. The analysis of I<sub>ds</sub>-V<sub>ds</sub> measurements provides detailed insights into the nature of the metal contacts, whether ohmic or Schottky. A comparative study of different contact types and their impact on the FET's performance has been conducted in detail, highlighting their influence on key device characteristics.

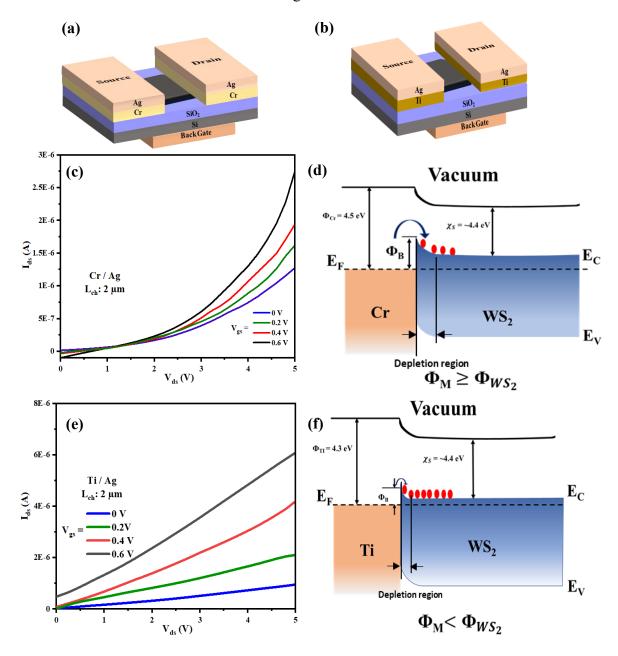

Fig. 5.7(a & b) illustrates the schematic representation of a back gated WS<sub>2</sub>-FET structure with Cr/Ag contact and Ti/Ag contact. The output characteristics of the WS<sub>2</sub>-FET, as shown in Fig. 5.7(c), demonstrate non-ohmic behaviour. A non-ohmic contact often signifies the presence of a SBH at the M-S interface, the schematic energy band diagram is depicted in Fig. 5.7(d) [33]. The high barrier height is formed due to the mismatch between the  $\chi_S$  and the  $\Phi_M$  [34]. Reported findings indicate that few-layer WS<sub>2</sub> forms n-type contacts when interfaced with low-work function of metals ( $\Phi_M < \Phi_{WS_2}$ ). In an ideal case, the barrier height is calculated as the difference between the  $\chi_S$  and  $\Phi_M$ . For WS<sub>2</sub>, the electron affinity varies from ~4.7 eV for a monolayer and ~4.4 eV for multilayers. Comparatively, the work functions of Cr ( $\Phi_{Cr}$ ) is 4.5 eV and Ti ( $\Phi_{Ti}$ ) is 4.3 eV, respectively [6, 35]. However, the work function of Cr is approximately equal to or slightly higher than the electron affinity of few-layer WS<sub>2</sub> nanosheets [36]. This minimal difference can restrict efficient electron injection across the metal-WS2 interface, potentially increasing the R<sub>C</sub> and SBH. In addition, the layered structure of WS<sub>2</sub>, along with the presence of numerous dangling bonds at the metal-WS2 interface, makes it more prone to defect states compared to bulk materials. These defect states result in Fermi-level pinning, causing the SBH to deviate from the theoretical predictions of the Schottky-Mott rule [37]. These factors can adversely impact the performance of FETs by reducing current flow and degrading the overall device efficiency. Despite the presence of a SBH, electrons at the source contact, induced by the gate bias, can facilitate field emission, reducing the depletion layer and increasing the tunneling current. As a result, the drain current  $I_{ds}$  increase as the  $V_{gs}$  is raised [38].

The output characteristics of the corresponding FET device exhibit nearly ohmic behaviour, as shown in Fig. 5.7(e). The Ti metal in contact with WS<sub>2</sub> in FET device signifies a low barrier height at the metal-semiconductor junction due to a thinner depletion layer as depicted in Fig.5.7(f). The FET with Ti/Ag contacts exhibits greater

drain current I<sub>ds</sub> compared to the Cr-contact-based FET, due to is low Schottky barrier and reduced contact resistance at the Ti/Ag interface.

Fig. 5.7: Schematic depiction of WS<sub>2</sub>-FET device structure with a channel length of  $\sim$ 2  $\mu$ m: (a) Cr/Ag metal contact and (b) Ti/Ag metal contact-based FET, (c) output characteristics ( $I_{ds}$ - $V_{ds}$ ) of Cr/Ag contact based WS<sub>2</sub> FET and (d) corresponding energy band diagram of Cr-WS<sub>2</sub> interfaces (e) output characteristics  $I_{ds}$ - $V_{ds}$  of the Ti/Ag contact based WS<sub>2</sub>-FET (f) energy band diagram of Ti-WS<sub>2</sub> interfaces

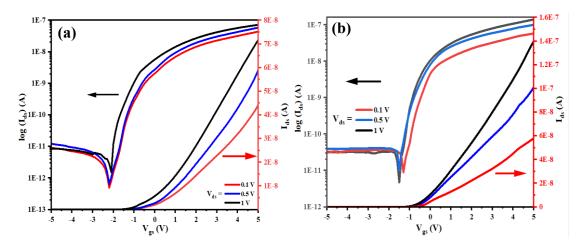

To assess the comprehensive performance of the device and obtain key electrical metrics, it is crucial to study the transfer characteristics of the FET. This involves plotting

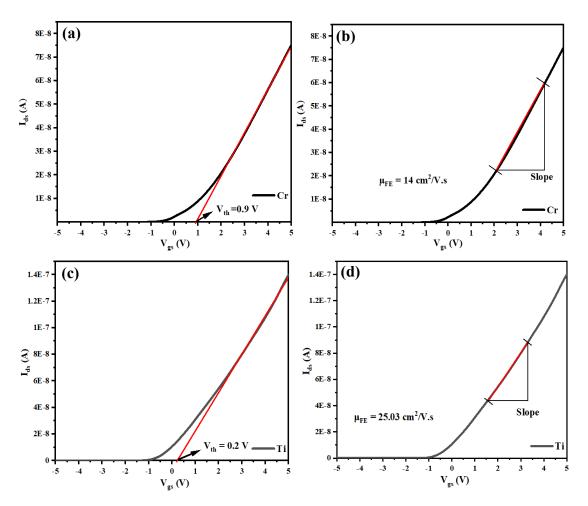

Ids as a function of gate voltage Vgs while keeping Vds constant, as shown in Fig. 5.8 (a & b) for Cr and Ti contact-based WS<sub>2</sub>-FET. Important parameters like V<sub>th</sub>, SS, and μ<sub>FE</sub> can be estimated by examining the transfer characteristics of the fabricated FETs. These parameters offer an understanding of the device's electrical characteristics, such as its I<sub>ON</sub>/I<sub>OFF</sub> ratio, current modulation, and the effectiveness of charge carrier movement through the WS<sub>2</sub> channel [39]. The V<sub>th</sub> of a transistor is generally defined as the point at which the drain current starts to diverge from its exponential behaviour in the subthreshold region as the gate-source voltage is increased [40]. The V<sub>th</sub> is a key parameter of FET, as it defines the device's switching characteristics and operating mode [41]. It determines the point at which the transistor transitions from the off state to the on state, making it essential for controlling current flow. Furthermore, there is a consistent trend between the values of V<sub>th</sub> and the observed on-currents, where a lower V<sub>th</sub> typically correlates with a higher on-current, highlighting the influence of threshold voltage on the device's performance. A noticeable positive V<sub>th</sub> on the positive side of the V<sub>gs</sub> axis is observed for all the FETs. The V<sub>th</sub> was derived through linear extrapolation of the device's transfer characteristics as demonstrated in Fig. 5.9(a & c) [42]. The extracted  $V_{th}$  of the WS<sub>2</sub>-FETs is ~0.9 V for the Cr contact and ~0.2 V for the Ti contact. This indicates that the Ti-WS2 contact exhibits a lower threshold voltage compared to the Cr contact. However, both the FET shows n-type FET characteristics.

Fig. 5.8: Transfer characteristics  $I_{ds}$ - $V_{gs}$  of the WS<sub>2</sub>-FET for (a) Cr/Ag metal contact and (b) Ti/Ag metal contact for channel length of  $\sim$ 2  $\mu$ m

Field-effect mobility is an essential parameter for FET that greatly influences the ON-state behaviour of the device. It assesses the velocity of charge carriers, such as electrons or holes travel through the transistor channel under an applied extremal bias

[43]. While intrinsic mobility is a fundamental material property determined by factors like crystal quality and scattering mechanisms,  $\mu_{FE}$  is influenced by extrinsic effects, such as  $R_C$  at M-S interface [44]. High contact resistance can hinder charge injection, reducing the effective mobility and limiting device performance. The  $\mu_{FE}$  represents a combination of the material's intrinsic properties and the device's practical constraints, highlighting the importance of optimizing both material quality and device design for improved performance. The  $\mu_{FE}$  is extracted from the slope of the transfer curve of the FET and it can vary with  $V_{ds}$ . It is calculated using the following equation [45]\_

$$\mu_{FE} = \frac{dI_{ds}}{dV_{gs}} \times \frac{L}{WV_{ds}C_{ox}}$$

(5.1)

Where,  $\frac{dI_{ds}}{dV_{gs}}$  represents transconductance (g<sub>m</sub>), L is the channel length and W is the channel width, and C<sub>ox</sub> is the Oxide Capacitance of the SiO<sub>2</sub>-coated Si substrate. Fig. 5.9(b & d) illustrates the extraction of transconductance g<sub>m</sub> from the slope of the I<sub>ds</sub>-V<sub>gs</sub> plot in the linear scale. The calculated data demonstrate that the WS<sub>2</sub>-FET device with a Cr metal contact exhibits a lower mobility of approximately 14 cm<sup>2</sup>/V·s at room temperature. In contrast, employing a Ti contact in the WS<sub>2</sub>-based FET enhances the mobility to around 25.03 cm<sup>2</sup>/V·s for a channel length of ~2 µm, which is significantly higher compared to the Cr contact. The above findings clearly emphasize the significance of proper contact formation in optimizing the intrinsic properties of novel nanomaterials and demonstrate that the mobility value is improved by the use of Ti contacts.

The subthreshold slope is a fundamental metric for quantifying the switching efficiency and performance of FETs. For the fabricated WS<sub>2</sub>-FET devices, the SS is determined from the  $log(I_{ds})$ -V<sub>gs</sub> plot, by extracting the slope from the linear region of the transfer curve. This region corresponds to the exponential increase in  $I_{ds}$  with gate voltage V<sub>gs</sub> when the device is transitioning from the off-state to the on-state. The estimated SS decreases from 0.6 V/dec for Cr contacts to 0.3 V/dec for Ti contacts. The SS is mathematically expressed by using the following equation [46]:

$$SS = \frac{d V_{gs}}{d \log I_{ds}}$$

$$= \ln 10 \frac{kT}{e} \left[ 1 + \frac{C_{it}}{C_{ox}} \right]$$

(5.2)

Where k is the Boltzmann Constant, T is the operating temperature, e is the charge of an electron, and  $C_{it}$  is capacitance related to the Interface Trap Density  $(D_{it}) \sim 1.2 \times 10^{11}$

eV<sup>-1</sup>.cm<sup>-2</sup> obtained by using the equation of  $(D_{it} = \frac{C_{it}}{e})$ . The presence of interface traps within the device can lead to an increased subthreshold swing, variability, and shift of the threshold voltage. A higher SS in the FET device requires a larger gate voltage to turn on the device.

**Fig. 5.9:** Determination of  $V_{th}$  from the  $I_{ds}$ - $V_{gs}$  plot of the WS<sub>2</sub>-FETs and extraction of  $g_m$  from the slope  $(g_m = \frac{dI_{ds}}{dV_{gs}})$  of the  $I_{ds}$ - $V_{gs}$  plot in linear scale for (a & b) Cr contact-based WS<sub>2</sub>-FET and (c & d) Ti contact-based WS<sub>2</sub>-FET

Nevertheless, the Ti-WS<sub>2</sub> FET with a  $L_{ch}$  of ~2 demonstrated a higher value of  $I_{ON}$  current. The higher ON current is conversely correlated with the high drive current, low  $V_{th}$  and SS value, which allows for improving the channel conductance of the WS<sub>2</sub> -FET device. The  $I_{ON}/I_{OFF}$  ratio of the fabricated FL-WS<sub>2</sub> FET, obtained from the transfer characteristics of the device, is approximately ~10<sup>4</sup>. This is determined by the ratio of the maximum current ( $I_{max}$ ) at  $V_{ds} = 1$  V to the minimum current ( $I_{min}$ ) observed in the transfer

characteristics of the FET at room temperature and  $I_{min}$  is the lowest average value of the FET [47].

Compared to Cr contact-based WS<sub>2</sub>-FETs, Ti contact-based devices exhibit superior performance characteristics, such as a lower threshold voltage, reduced subthreshold swing, and higher field-effect mobility. These results indicate that Ti-contact establishes a more efficient contact with WS<sub>2</sub> than Cr-contact, resulting in enhanced device performance. This improvement is primarily attributed to the lower work function of Ti compared to Cr [48]. The work function of a metal determines its ability to align the Fermi level at the metal-semiconductor interface. In the case of Ti, its lower work function places the Fermi level closer to the conduction band edge of WS<sub>2</sub>, as illustrated in Fig. 5.7(f). This closer alignment reduces the Schottky barrier height for electron injection at the interface, thereby enhancing the efficiency of charge injection into the WS<sub>2</sub> channel. The improved alignment facilitates better electron transport, allowing the device to operate at lower threshold voltages and with higher conductivity.

#### **5.3.3.** Channel Length Variation of the WS<sub>2</sub> -FET:

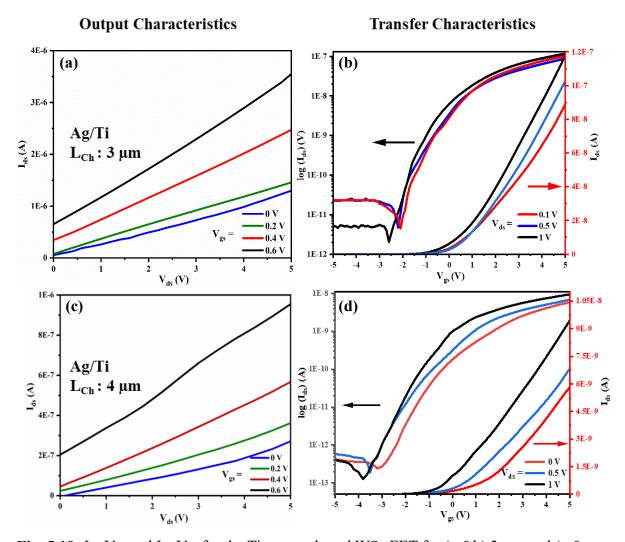

The effect of channel length scaling on the electrical properties of WS<sub>2</sub>-based FETs, including SS,  $V_{th}$ , On current ( $I_{on}$ ), and  $\mu_{FE}$ , was thoroughly examined. Fig.5.10 illustrates the output and transfer characteristics of WS<sub>2</sub>-FETs for channel lengths of 3  $\mu$ m and 4  $\mu$ m. Furthermore, the variation of the resultant output current ( $I_{ds}$ ) measured at a fixed  $V_{gs}$  and  $I_{on}$  current as a function of channel length is presented in Fig. 11(a & b) respectively. The  $I_{on}$  is extracted from their respective  $I_{ds}$ - $V_{gs}$  plot of FET. A notable observation is that the  $I_{ds}$  and  $I_{on}$  current decreases significantly as the channel length increases, compared to shorter channel lengths. In these plots, the  $I_{on}$  current is specifically the maximum value of  $I_{ds}$  observed when the transistor is fully turned on, typically occurring in the saturation region of the  $I_{ds}$ - $V_{gs}$  curve. The  $I_{on}$  current is a critical parameter that reflects the transistor's ability to conduct current when in the "on" state, which is directly linked to the device's switching performance and drive capabilities [39]. This trend highlights the critical role of channel length scaling in determining the device's electrical performance, which can be attributed to increased channel resistance and reduced charge carrier transport efficiency in longer channels.

In addition,  $V_{th}$ , SS and  $\mu_{FE}$  of the FETs were analyzed, across different channel lengths. As represented in 5.11(c),  $V_{th}$  tends to increase with increasing channel length.

This increase can be attributed to the reduced influence of short-channel effects. With longer channel lengths, the gate's electrostatic control over the channel becomes less susceptible to interference from the drain, requiring a higher gate voltage to establish conduction.

Fig. 5.10:  $I_{ds}$ - $V_{ds}$  and  $I_{ds}$ - $V_{gs}$  for the Ti contact based WS<sub>2</sub>-FET for (a &b) 3  $\mu m$  and (c & d) 4  $\mu m$  channel length

The SS and  $\mu_{FE}$  were also observed to vary with channel length. SS was found to increase with channel length, as illustrated in Fig. 5.11(d). A higher SS indicates a less efficient switching behaviour, demanding higher gate voltage to transition between states. This increase in SS with channel length can be attributed to the reduced ability of the gate to modulate the channel efficiently over longer distances. Similarly, the  $\mu_{FE}$ , also increases with channel length, as shown in Fig. 5.11(d). In longer channels, the effects of carrier scattering, velocity saturation, and other short-channel effects are diminished,

allowing for more efficient charge transport [39]. While longer channels improve  $\mu_{FE}$ , they also result in increased  $V_{th}$  and SS, which can negatively affect switching performance. These observations highlight the complex interplay between channel length and the electrical parameters, emphasizing the need to optimize channel dimensions for desired device performance [49].

Fig. 5.11: (a) Variation of drain current  $I_{ds}$  from output characteristics of WS<sub>2</sub>-FET with Ti contact (b) ON current of the FETs are plotted as a function of channel length (c) threshold voltage  $V_{th}$  extracted from the  $I_{ds}$ - $V_{gs}$  plot (d) calculated field effect mobility  $\mu_{FE}$  and subthreshold swing SS plotted as a function of channel length

## 5.3.4. Doping Effect in WS<sub>2</sub> FET:

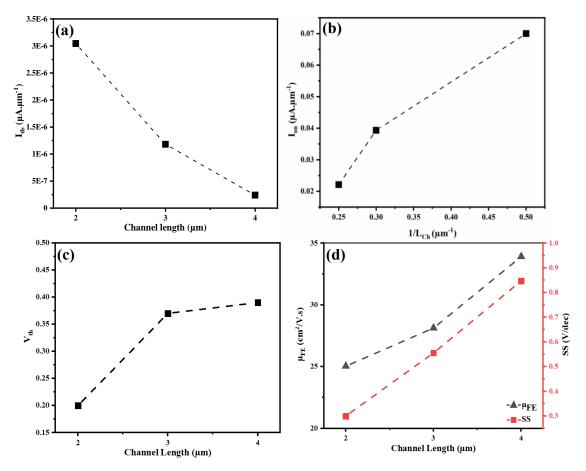

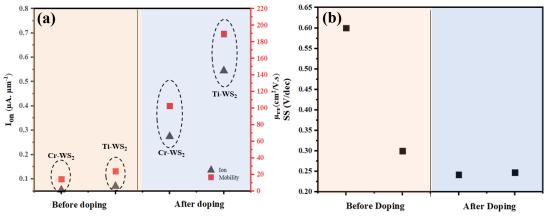

After doping the WS<sub>2</sub> nanosheet with an n-type dopant material, a notable shift in the electrical characteristics of the WS<sub>2</sub>-FET was observed, as illustrated in Fig. 5.12. The doping process was carried out on the WS<sub>2</sub> nanosheet surface through an absorption method, using chlorine (Cl) atoms as an n-type dopant. This n-type doping led to an increase in the drain current, which in turn enhanced the field-effect mobility. The dopant

atoms introduced interface defect states within the semiconductor, increasing the carrier concentration at the contact interface [50]. The detailed process of doping the WS<sub>2</sub> nanosheets is described in Chapter 4. This shift may have altered the Fermi level pinning position, leading to a reduction in the Schottky barrier height and contact resistance at the interface of Metal-Semiconductor [51].

In addition, key electrical parameters of the FET, such as field effect mobility, SS, and contact resistance, were calculated. After doping, the WS<sub>2</sub>-FET with Cr/Ag contacts exhibited improved conductivity, with the mobility and SS enhanced from ~14 cm<sup>2</sup>/V·s to ~102 cm<sup>2</sup>/V·s and 0.6 V/dec to 0.24 V/dec, respectively. The extracted data demonstrate that the device's ON current also increased due to doping, which facilitated the improvement of the carrier concentration through electron injection [51].

**Fig. 5.12:**  $I_{ds}$ - $V_{ds}$  and  $I_{ds}$ - $V_{gs}$  characteristics of the doped WS<sub>2</sub>-FET for channel length of  $2\mu m$ : (a & b) for Cr/Agr and (c & d) Ti/Ag contact

The extracted data reveal that doping significantly enhances the device's performance by increasing the ON current. This improvement is attributed to the increased carrier concentration facilitated through electron injection, as doping introduces additional charge carriers into the channel [52]. The doping process effectively modifies the material's electrical properties, enabling better current conduction when the transistor is in the "on" state. As shown in Fig. 5.13(a), the variations in  $\mu_{FE}$  and  $I_{on}$  are plotted for doped and undoped devices using both Ti and Cr contacts, with a  $I_{Ch}$  of 2  $\mu_{II}$ . The results clearly demonstrate an increase in both  $I_{FE}$  and  $I_{on}$  for doped devices, regardless of the contact material. This increase can be explained by the enhanced carrier transport efficiency due to higher carrier concentration. The presence of additional dopants reduces the scattering and trapping of charge carriers, thereby facilitating smoother charge transport and leading to an improvement in the device's electrical performance [33]. The enhancement is consistent across devices with Ti and Cr contacts, indicating that doping plays a dominant role in improving mobility and drive current. In addition, a notable reduction in the SS of the FETs is observed after doping as demonstrated in Fig. 5.13(b)

**Fig. 5.13:** (a)  $I_{on}$  and field-effect mobility  $\mu_{FE}$  for undoped and doped WS<sub>2</sub>-based FET and (b) SS for undoped and doped WS<sub>2</sub>-based FET

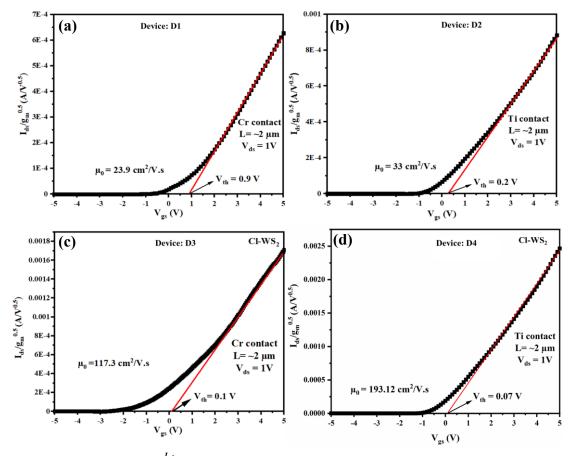

# 5.3.5. Measurement of Threshold Voltage and Intrinsic Mobility Using Y-Function Method:

The primary obstacle in elucidating intrinsic charge transport properties in low-dimensional materials, such as 2D layered materials, is the considerable R<sub>C</sub> typically present at M-S interface [53]. This contact resistance can hinder the material's true electrical properties, making accurate characterization difficult [54]. However, the Y-

function method provides a way to extract contact resistance, threshold voltage, and intrinsic mobility of FETs [55]. Initially, the Y-function proposed by Ghibaudo et.al., method is used for extracting Intrinsic Mobility ( $\mu_0$ ) and  $V_{th}$  in silicon-based transistor devices [56]. The Y-function method describes the transconductance or two-point conductance of field-effect devices, which is defined as  $I_{ds}/\sqrt{g_m}$ , where  $I_{ds}$  is the drain current and  $g_m$  is the transconductance of the FET extracted from the  $I_{ds}$ - $V_{gs}$  characterization at a constant  $V_{ds}$  [57]. This approach is particularly useful for studying device physics, as it effectively isolates the intrinsic mobility by excluding the influence of contact resistance. Additionally, the Y-function analysis enables the simultaneous extraction of both the threshold voltage and the effective contact resistance of individual devices.

The Y-function method is a widely used approach for extracting key device parameters in field-effect transistors. It is based on the analysis of the  $I_{ds}$  in the linear region of the  $I_{ds}$ - $V_{gs}$  characteristics at a constant  $V_{ds}$ . The drain current in this region can be described by the following equation [57]\_

$$I_{ds} = \frac{W.C_{ox}.\mu_{FE}.(V_{gs}-V_{th}).V_{ds}}{L}$$

$$= \left[\frac{W.C_{ox}.(V_{gs}-V_{th}).V_{ds}}{L}\right].\left[\frac{\mu_{0}}{1+\theta.(V_{gs}-V_{th})}\right]$$

(5.3)

Here,  $\mu_0$  denotes the intrinsic mobility,  $\theta$  is mobility attenuation coefficient, incorporates the effects of carrier scattering and surface defects to better represent realistic device performance. Fig. 5.14 plots represent the Y-function method as a function of  $V_{gs}$  at constant  $V_{ds}$  is defined by [58]\_

$$Y = \frac{I_{ds}}{\sqrt{g_m}}$$

$$= \sqrt{I_{ds}} \cdot \sqrt{(V_{gs} - V_{th}) \cdot \{1 + \theta \cdot (V_{gs} - V_{th})\}}$$

$$= \sqrt{\frac{W \cdot \mu_0 \cdot C_{ox} \cdot V_{ds}}{L}} \cdot (V_{gs} - V_{th})$$

(5.4)

Where  $g_m$  is the transconductance defined as  $dI_{ds}/dV_{gs}$  is extracted from the slope of  $I_{ds}-V_{gs}$  plot in linear scale at constant  $V_{ds}$ . The presence of Schottky barriers at the source and drain contacts introduces a  $V_{gs}$  dependence in the  $R_C$ . This dependence is taken into account when calculating  $dI_{ds}/dV_{gs}$ . The  $\mu_0$  is extracted from the slope of the Y-function by extrapolating the  $\frac{I_{ds}}{\sqrt{g_m}}$  vs.  $V_{gs}$  curve at a constant drain-source voltage ( $V_{ds}$  =

1 V), independent of the attenuating factors. This method ensures that the extracted  $\mu_0$  remains unaffected by attenuating factors such as variations in contact resistance or the presence of Schottky barriers, providing a more accurate characterization of the intrinsic device properties. The extracted threshold voltage  $V_{th'lin}$  from the linear extrapolation of the  $I_{ds}$ - $V_{gs}$  plot and the  $V_{th'Y}$  obtained from the Y-function method are expected to be the same, as both aim to determine the point where the channel starts conducting as shown in Fig. 14(a-d). The devices are denoted by: D1 (Cr-contact WS<sub>2</sub>-FET), D2 (Ti-contact WS<sub>2</sub>-FET), D3 (Cr-contact Cl-doped WS<sub>2</sub>-FET), and D4 (Ti-contact Cl-doped WS<sub>2</sub>-FET).

The  $\theta$  can be described by the following equation [58]

$$\theta = \theta_{Ch} + \frac{W.\mu_0.C_{ox}R_C}{L} \tag{5.5}$$

Where  $\theta_{Ch}$  is the mobility attenuation factor from the channel, which includes effects such as a surface roughness and phonon scattering assumed to be negligible [59].

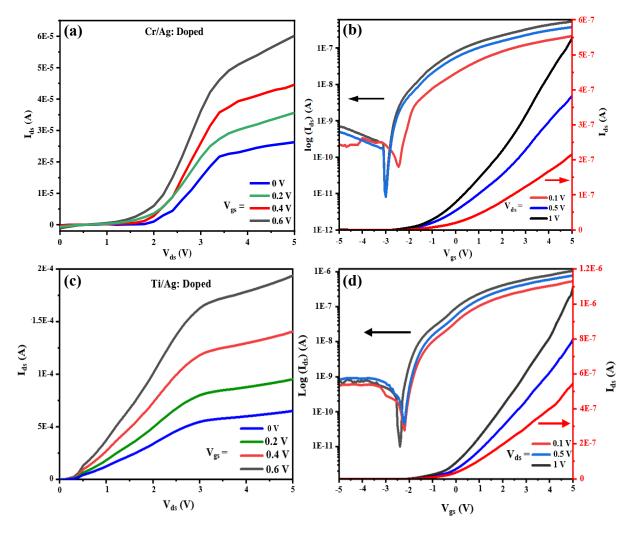

**Fig. 5.14:** Y-Function  $(\frac{I_{ds}}{\sqrt{g_m}})$  plotted as a function of  $V_{gs}$  at constant  $V_{ds}$  for devices: (a) D1: Cr contact (b) D2: Ti contact and (c) D3- Cr contact with Doped WS<sub>2</sub> and (d) D4: Ti contact with Doped WS<sub>2</sub>-FET and  $V_{th}$  is extracted from the x-axis intercept of the linear fit of the characteristics curve

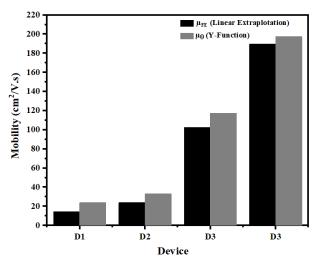

Fig. 5.15 presents a comparative analysis of the mobility values obtained using two distinct extraction methods:  $\mu_0$ , derived from the Y-function method, and  $\mu_{FE}$ , extracted from the linear regime of the  $I_{ds}$ - $V_{gs}$  characteristics at a constant  $V_{ds}$ . The results indicate that  $\mu_0$  is consistently higher than the measured  $\mu_{FE}$ , underscoring the differences between these two approaches in evaluating carrier transport efficiency within the device. Notably, the  $\mu_0$  values for the Cr and Ti contact-based contacts have improved to 23.9 cm²/V.s and 33.04 cm²/V.s, respectively. These values are significantly higher than the corresponding  $\mu_{FE}$  values of 14 cm²/V.s and 25.03 cm²/V.s, demonstrating that the Y-function method ( $\mu_0$ ) suggests a more efficient carrier transport compared to the linear regime-based method ( $\mu_{FE}$ ). This contrast highlights the influence of the measurement techniques on the assessment of device performance.

Fig. 15: Comparison of field-effect mobility (extracted from linear extrapolation of  $I_{ds}$ - $V_{gs}$  and intrinsic mobility (calculated using the Y-function method) for doped and undoped WS<sub>2</sub>-based FETs. Devices: D1 (Cr contact), D2 (Ti contact), D3 (Cr contact with doping), and D4 (Ti contact with doping).

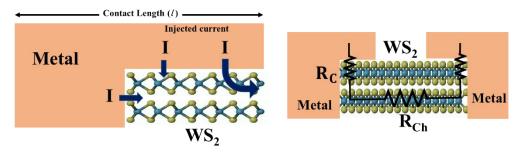

#### 5.3.6. Measurement of Contact Resistance at the Metal-WS<sub>2</sub> Interface:

The conduction mechanism through the Metal-Semiconductor junction of the back-gated 2D WS<sub>2</sub> FET has been studied. In the 2D-FET, the semiconductor thickness is typically smaller than the depletion width, leading to a different conduction mechanism compared to the traditional model. The current flow mechanism in the M-WS<sub>2</sub> junction for back-gated FET where the metal contact is made on the WS<sub>2</sub> thin film is schematically depicted in Fig. 5.16. The arrow represents the current flow through the junction of the M-

S interface where the electrostatically induced electron (e<sup>-</sup>), is injected from the metal to WS<sub>2</sub>.

**Fig. 5.16:** The path of current flow from metal to WS<sub>2</sub> in the FET device is schematical illustrated

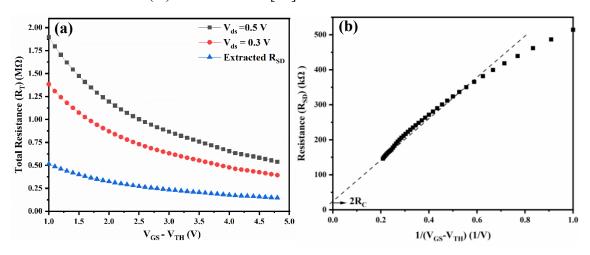

TLM, is a widely used technique for evaluating the contact resistance of FETs. However, its application can be challenging, as it requires multiple transistors with varying channel lengths and uniform contact properties to achieve accurate and reliable results. Additionally, local defects on the material's surface can introduce noticeable variations, leading to inconsistencies in the measurements. To address this limitation, the simple Series Resistance Extraction Methodology procedure was determined using the ratio of two I<sub>ds</sub>-V<sub>gs</sub> curves measured under two different drain bias conditions [60]. This method is simple and efficient, as it requires only two linear transfer curves from a single device. To examine the impact of the type of material used as metal contact and doping in semiconductors, on  $R_C$ , the total resistance ( $R_T = V_{ds}/I_{ds}$ ) of the device as a function of gate overdrive for the two drain biases ( $V_{ds} = 0.3$  and 0.5 V) is determined in Fig. 5.17(a). The R<sub>T</sub> represents the sum of the series resistance (R<sub>SD</sub>) and Channel Resistance (R<sub>Ch</sub>), where R<sub>SD</sub> is equal to 2R<sub>C</sub> can be extracted using two different channel resistance values at a high overdrive bias [61]. The calculated R<sub>SD</sub> value is extrapolated as a function of  $1/(V_{gs}-V_{th})$ , and the R<sub>C</sub> is obtained from the R<sub>SD</sub> vs.  $1/(V_{gs}-V_{th})$  curve, the R<sub>C</sub> extraction is represented in Fig. 5.17(b) [62]. It was observed that a higher R<sub>T</sub> correlates with lower I<sub>ds</sub> and reduced channel conductivity. Results show that a ~2 μm channel length with Ti contacts yields the highest I<sub>ds</sub>, effectively reducing R<sub>C</sub>. Additionally, higher R<sub>T</sub> values may be attributed to factors such as increased R<sub>C</sub> at the Metal-WS<sub>2</sub> interface and reduced conductivity, both of which hinder charge transport in the device [63].

$$R_{T} = R_{SD} + R_{Ch}$$

$$R_{SD} = 2R_{C}$$

$$[5.6]$$

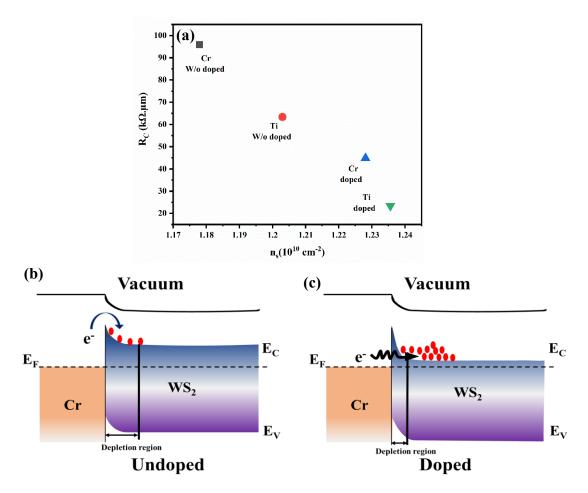

The extracted  $R_C$  for Ti and Cr are 63.04  $k\Omega.\mu m$  and 91.79  $k\Omega.\mu m$  respectively for ~2  $\mu m$  channel length which is comparatively lower than Cr contact-based FET device. After doping the WS<sub>2</sub> surface for a Cr contact-based FET device, the  $R_C$  decreased significantly from 91.79  $k\Omega.\mu m$  to 44.82  $k\Omega.\mu m$ . This notable reduction in  $R_C$  indicates that the increased carrier concentration can enhance the operating performance of the FET and lower the barrier height at the M-S contact facilitating the narrow tunnel barrier [64]. The results demonstrated that the  $R_C$ ,  $R_T$  and  $R_{Ch}$  is strongly depend on the carrier concentration ( $n_s$ ) of the channel [38].

Fig. 5.17: (a)  $R_T$  at different  $V_{ds}$  for extraction of series resistance  $R_{SD}$  and (b) the distribution of the  $R_{SD}$  value plotted against  $1/(V_{gs}-V_{th})$  for the extraction of  $2R_C$

In addition, the carrier concentration  $(n_s)$  of the FETs was calculated for both doped and undoped WS<sub>2</sub>-based FETs. The  $n_s$  was calculated using the following equation [65]

$$n_s = \frac{(V_{gs} - V_{th}) \cdot C_{ox}}{q}$$

[5.7]

The carrier concentration of the FET channel can be modulated by the applied gate voltage. The concentration of the charge carrier depends on various other factors such as channel conductivity and interface engineering of source-drain metal contacts which can strongly affect the operating performance of FET. It reduces the barrier width at the junction by applying a back-gate voltage, facilitating carrier tunnelling through the barrier and consequently decreasing the contact resistance R<sub>C</sub>. In this case doping is studied to vary carrier concentration. The extracted value of R<sub>C</sub> for all the FETs is plotted as a function of carrier concentration n<sub>s</sub> is depicted in Fig. 5.18(a). The n<sub>s</sub> of both the Crand Ti-contact-based FETs show 1.18 x 10<sup>10</sup> cm<sup>-2</sup> and 1.20 x 10<sup>10</sup> cm<sup>-2</sup>, which improve to

$1.23 \times 10^{10} \ cm^{-2}$  and  $1.25 \times 10^{10} \ cm^{-2}$  respectively. The increase in carrier concentration facilitates the decrease in contact resistance after doping. The obtained results demonstrate that the charge carrier concentration is inversely proportional to the contact resistance. As the carrier concentration increases, a corresponding decrease in contact resistance is observed after doping. A lower  $R_C$  at the M-S interface facilitates easier electron flow through the junction.

**Fig. 5.18:** (a) Variation of R<sub>C</sub> with n<sub>s</sub> for both doped and undoped WS<sub>2</sub>-FETs and (b & c) energy band diagram of Metal-WS<sub>2</sub> interface for undoped and doped WS<sub>2</sub>-based FET

Additionally, the data reveals that n-type doping significantly facilitates the flow of electrons through the junction of the FET [66]. By introducing charge carriers into the semiconductor, the doping process enhances the carrier concentration, making it easier for electrons to flow across the junction [51]. This increased carrier concentration also plays a crucial role in modulating the conduction band, causing it to move closer to the Fermi level as shown in Fig. 5.18(c). As a result, the material's electronic properties are altered, leading to improved conductivity. The enhanced electron flow is primarily

enabled by two mechanisms: tunnelling and Fermi-level pinning. Tunneling allows electrons to pass through potential barriers at the metal-semiconductor interface, even without overcoming the barrier's full energy requirement. This phenomenon effectively narrows the width of the depletion layer at the M-S interface. A narrower depletion layer allows for easier electron movement, improving the efficiency of carrier transport across the junction. These findings demonstrate that the reduction in depletion layer width through doping not only enhances the electron flow but also optimizes the performance of the FET by facilitating more efficient electron conduction [43,44]. The fabricated WS2-FET exhibits promising electrical characteristics, including enhanced mobility, reduced R<sub>C</sub> and other electrical parameters, through doping on WS<sub>2</sub> nanosheets and improved carrier transport facilitated by appropriate metal contacts. A key concern is the susceptibility of WS<sub>2</sub>-FET to environmental factors such as humidity and temperature, which can lead to degradation of its electrical performance over time. The future work prioritizing this dimension to address the issue of environmental robustness, long-term stability, and scalability of WS<sub>2</sub>-FET will pave the way for the commercial viability of the technology.

### 5.4. Summary:

The fabricated few layer-WS<sub>2</sub> back-gated FET device demonstrated stable electrical performance following a two-step lithography process, confirming that the fabrication steps did not significantly impact the crystalline structure of WS<sub>2</sub>. However, the Cr metal contact with the WS<sub>2</sub> nanosheet displayed non-linear characteristics due to high contact resistance, arising from the mismatch between the metal's work function and the semiconductor's electron affinity. A comprehensive analysis of the electrical characteristics of the fabricated FL-WS<sub>2</sub> FETs was conducted. The study showed that factors like metal contacts (Cr and Ti), variations in channel length, and doping considerably influenced key electrical parameters of FL-WS<sub>2</sub> FETs, such as  $\mu_{FE}$ ,  $V_{th}$ , subthreshold swing, ON current, contact resistance, and overall device conductivity. Our findings indicate that the Cr-WS<sub>2</sub> FET exhibited a mobility of approximately 14.3 cm<sup>2</sup>/V·s, which improved to around 25.03 cm<sup>2</sup>/V·s with Ti contacts for a channel length of about 2  $\mu$ m. After doping, the mobility further increased significantly, reaching approximately 102.7 cm<sup>2</sup>/V·s for Cr-contact-based WS<sub>2</sub> FETs and ~189.5 cm<sup>2</sup>/V·s for Ti-contact-based WS<sub>2</sub> FETs, demonstrating the effectiveness of doping in enhancing carrier

transport properties. Additionally, the SS values for all FETs were higher than those for Ti-WS<sub>2</sub>-FETs and doped WS<sub>2</sub> FETs, with a minimum value of 0.2 V/dec. However, all FETs show the  $I_{ON}/I_{OFF}$  ratio is ~ $10^4$  with n-type FET characteristics. In addition, the Y-function method has proven to be an accurate and robust approach for extracting the intrinsic mobility of FETs, even when accounting for the gate-dependent variations commonly observed in semiconducting TMD transistor devices. The Y-function analysis mentioned in section 5.3.6 indicates that the  $\mu_0$  of the FET is higher compared to  $\mu_{FE}$ . However, the threshold voltage of the FETs remains unchanged in the Y-function analysis. It was observed that the shorter channel lengths led to higher drain currents, facilitated by contact engineering with the low-work-function metal like Ti. The contact resistance of the Cr-contact-based WS<sub>2</sub> FET decreased from 91.7 k $\Omega$ · $\mu$ m to 44.82 k $\Omega$ · $\mu$ m with n-type doping, while the Ti-contact-based FET exhibited a reduction from 63.34 k $\Omega$ · $\mu$ m to 23.39 k $\Omega$ · $\mu$ m after doping. The highest carrier concentration (n<sub>s</sub>) was 1.25 x  $10^{10}$  cm<sup>-2</sup>, and the V<sub>th</sub> was approximately 0.07 V for the fabricated FET with Ti contact. These results indicate that 2D WS<sub>2</sub> is a promising material for FET applications.

#### **Bibliography:**

- [1] Sun, Z., et al. Statistical Assessment of High-Performance Scaled Double-Gate Transistors from Monolayer WS<sub>2</sub>. ACS Nano., 16(9):14942–50, 2022.

- [2] Majumder, S.,et al. Chemistry and Interfacial Structure Promoting Quasi-van der Waals Epitaxial Growth of WS2 Nanosheets on Sapphire for Prospective Application in Field-Effect Transistors. ACS Appl. Nano Mater. 8(18): 9256–9267, 2025.

- [3] Yadav, P.V.K. & Ashok Kumar Reddy, Y. Controlled two-step synthesis of nanostructured WS<sub>2</sub> thin films for enhanced UV-visible photodetector applications. Sensors and Actuators A: Physical., 345:113780, 2022.

- [4] Acar, M., et al. Single-step, large-area, variable thickness sputtered WS<sub>2</sub> film-based field effect transistors. Ceramics International., 46(17):26854–26860, 2020.

- [5] Aji, A.S., et al. High Mobility WS<sub>2</sub> Transistors Realized by Multilayer Graphene Electrodes and Application to High Responsivity Flexible Photodetectors. Adv Funct Materials., 27(47):1703448, 2017.

- [6] Phan, N.A.N., et al. Enhanced Performance of WS<sub>2</sub> Field-Effect Transistor through Mono and Bilayer h-BN Tunneling Contacts. Small, 18(13):2105753, 2022.

- [7] Chen, M., et al. Sublimation-based wafer-scale monolayer WS<sub>2</sub> formation *via* self-limited thinning of few-layer WS<sub>2</sub>. Nanoscale Horiz. 9(1):132–142, 2024.

- [8] Pang, C.-S., et al. Thickness-Dependent Study of High- Performance WS<sub>2</sub>-FETs With Ultrascaled Channel Lengths. IEEE Trans. Electron Devices, 68(4):2123–2129, 2021.

- [9] Jia, X., et al. Weak interlayer interaction and enhanced electron mobility in multilayer WS<sub>2</sub> achieved through a layer-by-layer wet transfer approach. J Mater Sci., 59(29):13591–13601, 2024.

- [10] Muoi, D., et al. Electronic properties of WS<sub>2</sub> and WSe<sub>2</sub> monolayers with biaxial strain: A first-principles study. Chemical Physics., 519:69–73, 2019.

- [11] Han, T., et al. Preparation and Research of Monolayer WS<sub>2</sub> FETs Encapsulated by h-BN Material. Micromachines, 12(9):1006, 2021.

- [12] Jian, L., et al. WS<sub>2</sub> lateral p—n homojunction toward a sensitive self-driven photodetector by water treatment. Applied Physics Letters., 124(9):093506, 2024.

- [13] Gong, Y., et al. High flex cycle testing of CVD monolayer WS<sub>2</sub> TFTs on thin flexible polyimide. 2D Mater., 3, 3(2):021008, 2016.

- [14] Liu, X., et al. Investigation of chemical vapour deposition MoS<sub>2</sub> field effect transistors on SiO<sub>2</sub> and ZrO<sub>2</sub> substrates. Nanotechnology, 28(16):164004, 2017.

- [15] Iqbal, M.W., et al. High-mobility and air-stable single-layer WS<sub>2</sub> field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films. Sci Rep., 5(1):10699, 2015.

- [16] Zeissler, K. Wafer-scale transfer of tungsten disulfide. Nat Electron., 5(7):410–410, 2022.

- [17] Jin, L., et al. High-Performance WS<sub>2</sub> MOSFETs with Bilayer WS<sub>2</sub> Contacts. ACS Omega, 9(29):32159–32166, 2024.

- [18] Yang, R., et al. Multilayer MoS<sub>2</sub> transistors enabled by a facile dry-transfer technique and thermal annealing. Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena, 32(6):061203, 2014.

- [19] Li, M.-Y., et al. Wafer-Scale Bi-Assisted Semi-Auto Dry Transfer and Fabrication of High-Performance Monolayer CVD WS<sub>2</sub> Transistor. In: 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). pp. 290–291. IEEE, Honolulu, HI, USA (2022).

- [20] Illarionov, Yu., et al. Process implications on the stability and reliability of 300 mm FAB MoS<sub>2</sub> field-effect transistors. npj 2D Mater Appl., 8(1):8, 2024.

- [21] Choi, K., et al. Trap density probing on top-gate MoS<sub>2</sub> nanosheet field-effect transistors by photo-excited charge collection spectroscopy. Nanoscale, 7(13):5617–5623, 2015.

- [22] Lan, C., et al. The origin of gate bias stress instability and hysteresis in monolayer WS<sub>2</sub> transistors. Nano Res., 13(12):3278–3285, 2020.

- [23] Gao, Q., et al. Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS<sub>2</sub> Transistors. Nanomaterials. 11, 1594 (2021.

- [24] Lin, D., et al. Dual gate synthetic WS<sub>2</sub> MOSFETs with 120μS/μm Gm 2.7μF/cm<sup>2</sup> capacitance and ambipolar channel. In: 2020 IEEE International Electron Devices Meeting (IEDM). p. 3.6.1-3.6.4. IEEE, San Francisco, CA, USA (2020).

- [25] Chen, T., et al. Homogeneous dual-gate MoS<sub>2</sub> field-effect transistors integrated by atomic layer deposition-based film synthesis. J Mater Sci: Mater Electron., 31(7):5485–5491, 2020.

- Cui, Y., et al. High-Performance Monolayer WS<sub>2</sub> Field-Effect Transistors on High-к Dielectrics. Advanced Materials., 27(35):5230–5234, 2015.

- [27] Jung, D.H., et al. Top-gate field-effect transistor based on monolayer WS<sub>2</sub> with an ion-gel gate dielectric. Jpn. J. Appl. Phys., 61(3):034001, 2022.

- [28] Marquez, C., et al. Performance and reliability in back-gated CVD-grown MoS<sub>2</sub> devices. Solid-State Electronics., 186:108173, 2021.

- [29] Jeffery, A., et al. Two-Dimensional Nanosheets and Layered Hybrids of MoS<sub>2</sub> and WS<sub>2</sub> through Exfoliation of Ammoniated MS<sub>2</sub> (M = Mo,W). J. Phys. Chem. C., 118(2):1386–1396, 2014.

- [30] Huang, F., et al. Few-layer thick WS<sub>2</sub> nanosheets produced by intercalation/exfoliation route. J Mater Sci., 51(22):10160–10165 (2016.

- [31] Iqbal, M.W., et al. Tailoring the electrical and photo-electrical properties of a WS<sub>2</sub> field effect transistor by selective n-type chemical doping. RSC Adv., 6(29):24675–24682, 2016.

- [32] Barbosa, A.D.N., et al. Photoluminescence quenching of CVD grown WS<sub>2</sub> monolayers treated with low-power Ar plasma. Surfaces and Interfaces., 33:102220, 2022.

- [33] Kim, J., An, et al. Comparative analysis of Schottky barriers for heterogeneous defect domains in monolayer WS<sub>2</sub> field-effect transistors. Applied Surface Science., 604: 154600, 2022.

- [34] Chen, S., et al. Latest advance on seamless metal-semiconductor contact with ultralow Schottky barrier in 2D-material-based devices. Nano Today., 42:101372, 2022.

- [35] Chen, X., et al. Probing the electron states and metal-insulator transition mechanisms in molybdenum disulphide vertical heterostructures. Nat Commun., 6(1):6088, 2015.

- [36] Sun, J., et al. Lateral 2D WSe<sub>2</sub> p–n Homojunction Formed by Efficient Charge-Carrier-Type Modulation for High-Performance Optoelectronics. Advanced Materials., 32(9):1906499, 2020.

- [37] Sotthewes, K., et al. Universal Fermi-Level Pinning in Transition-Metal Dichalcogenides. J. Phys. Chem. C., 123(9):5411–5420, 2019.

- [38] Zhang, S., et al. Control of the Schottky barrier height in monolayer WS<sub>2</sub> FETs using molecular doping. AIP Advances., 12(8):085222, 2022.

- [39] Sebastian, A., et al. Benchmarking monolayer MoS<sub>2</sub> and WS<sub>2</sub> field-effect transistors. Nat Commun., 12(1):693, 2021.

- [40] Yoo, G., et al. Enhancement-mode operation of multilayer MoS<sub>2</sub> transistors with a fluoropolymer gate dielectric layer. Applied Physics Letters., 108(26):263106, 2016.

- [41] Kaushik, V., et al. Charge Transport in 2D MoS<sub>2</sub>, WS<sub>2</sub>, and MoS<sub>2</sub>–WS<sub>2</sub> Heterojunction-Based Field-Effect Transistors: Role of Ambipolarity. J. Phys. Chem. C., 124(42):23368–23379, 2020.

- [42] Shen, T., et al. High mobility monolayer MoS<sub>2</sub> transistors and its charge transport behaviour under E-beam irradiation. J Mater Sci., 55(29):14315–14325, 2020.

- [43] Ovchinnikov, D., et al. Electrical Transport Properties of Single-Layer WS<sub>2</sub>. ACS Nano, 8(8):8174–8181, 2014.

- [44] Wang, Y., et al. Electron mobility in monolayer WS<sub>2</sub> encapsulated in hexagonal boron-nitride. Applied Physics Letters., 118(10):102105, 2021.

- [45] Liang, J., et al. Electron Transport Properties of WS<sub>2</sub> Field-Effect Transistors Modulated by Electron Beam Irradiation Under Gate Voltage. IEEE Electron Device Lett., 40(9):1542–1545, 2019.

- [46] Park, W., et al. Contact resistance reduction using Fermi level de-pinning layer for MoS<sub>2</sub> FETs. In: 2014 IEEE International Electron Devices Meeting. p. 5.1.1-5.1.4. IEEE, San Francisco, CA, USA (2014).

- [47] Shi, X., et al. Ultrashort channel chemical vapor deposited bilayer WS<sub>2</sub> field-effect transistors. Applied Physics Reviews., 10(1):011405, 2023.

- [48] Durán Retamal, J.R., et al. Charge carrier injection and transport engineering in two-dimensional transition metal dichalcogenides. Chem. Sci., 9(40):7727–7745, 2018.

- [49] Nasr, J.R., et al. Mobility Deception in Nanoscale Transistors: An Untold Contact Story. Advanced Materials, 31(2):1806020, 2019.

- [50] Yang, L., et al. Chloride Molecular Doping Technique on 2D Materials: WS<sub>2</sub> and MoS<sub>2</sub>. Nano Lett., 14(11):6275–6280, 2014.

- [51] Liu, M., et al. Enhanced carrier transport by transition metal doping in WS<sub>2</sub> field effect transistors. Nanoscale., 12(33):17253–17264, 2020.

- [52] Tang, B., et al. Direct n- to p-Type Channel Conversion in Monolayer/Few-Layer WS<sub>2</sub> Field-Effect Transistors by Atomic Nitrogen Treatment. ACS Nano, 12(3):2506–2513, 2018.

- [53] Liu, W., et al. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe<sub>2</sub> Field Effect Transistors. Nano Lett., 13(5):1983–1990, 2013.

- [54] Fleury, D., et al. New Y-function-based methodology for accurate extraction of electrical parameters on nano-scaled MOSFETs. In: 2008 IEEE International Conference on Microelectronic Test Structures. pp. 160–165. IEEE, Edinburgh, UK (2008).

- [55] Xu, Y., et al. Direct evaluation of low-field mobility and access resistance in pentacene field-effect transistors. Journal of Applied Physics, 107(11):114507, 2010.

- [56] Ghibaudo, G. New Method for the Extraction of MOSFET Parameters. Electron. Lett., 24:543-545, 1988.

- [57] Chang, H.-Y., et al. On the mobility and contact resistance evaluation for transistors based on MoS<sub>2</sub> or two-dimensional semiconducting atomic crystals. Applied Physics Letters., 104(11):113504, 2014.

- [58] Bhattacharjee, S., et al. Intrinsic Limit for Contact Resistance in Exfoliated Multilayered MoS<sub>2</sub> FET. IEEE Electron Device Lett., 37(1):119–122, 2016.

- [59] Na, J., et al. Separation of interlayer resistance in multilayer MoS<sub>2</sub> field-effect transistors. Applied Physics Letters., 104(23):233502, 2014.

- [60] Campbell, J.P., et al. A Simple Series Resistance Extraction Methodology for Advanced CMOS Devices. IEEE Electron Device Lett., 32(8):1047–1049, 2011.

- [61] Kim, Y., et al. Reduction of low-frequency noise in multilayer MoS<sub>2</sub> FETs using a Fermi-level depinning layer. Physica Rapid Research Ltrs., 10(8):634–638, 2016.

- [62] Kim, Y.J., et al. Contact Resistance Reduction of WS<sub>2</sub> FETs Using High-Pressure Hydrogen Annealing. IEEE J. Electron Devices Soc., 6:164–168, 2018.

- [63] Giza, M., et al. Contact Resistance Engineering in WS<sub>2</sub> -Based FET with MoS<sub>2</sub> Under-Contact Interlayer: A Statistical Approach. ACS Appl. Mater. Interfaces., 16(36):48556–48564, 2024.

- [64] Kang, J., Liu, W., Sarkar, D., Jena, D., Banerjee, K.: Computational Study of Metal Contacts to Monolayer Transition-Metal Dichalcogenide Semiconductors. Phys. Rev. X., 4(3):031005, 2014.

- [65] Wei, A., et al. A Novel Method to Extract Channel Mobility and Parasitic Resistance of 2-D Material MOSFETs. IEEE Trans. Electron Devices, 71(10):6424–6429, 2024.

- [66] Sunwoo, H., & Choi, W. Tunable, stable, and reversible n-type doping of MoS<sub>2</sub> via thermal treatment in N-methyl-2-pyrrolidone. Nanotechnology., 33(50):50LT01, 2022.

- [67] Murali, K., et al. Accurate Extraction of Schottky Barrier Height and Universality of Fermi Level De-Pinning of van der Waals Contacts. Adv Funct Materials., 31(18):2010513, 2021.