× 283

# GENTRAL LIBRARY

TEZPUR UNIVERS.T'.

Accession No. <u>T-283</u>

Date\_21/7/14

THESES & DISSERTATION SECTION CENTRAL LIBRARY, T.U.

## Study of Multi-Channel Spread Spectrum Systems for Wireless Communication

A thesis submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> By Mr. Mahipal Singh Reg. No.: 007/2013

Under the Supervision

Prof. Partha Pritam Sahu

Department of Electronics and Communication Engineering, School of Engineering Tezpur University Tezpur, Assam India -784028 October 2013

## **Dedicated** to

The Almighty and My Family Members

#### **AUTHOR'S DECLARATION**

I hereby declare that the thesis entitled "Study of Multi-Channel Spread Spectrum Systems for Wireless Communication" is an outcome of my research carried out at the Department of Electronics & Communication Engineering, School of Engineering, Tezpur University, Assam, India. The work is original and has not been submitted in part or full, for any degree or diploma of any other University or Institute.

Mahipal Singh)

Date: 31 Mar 2014

## **TEZPUR UNIVERSITY** Certificate

This is to certify that the thesis entitled "Study of Multi-Channel Spread Spectrum Systems for Wireless Communication" submitted to the Tezpur University in the Department of Electronics and Communication Engineering under the School of Engineering in partial fulfillment for the award of the degree of Doctor of Philosophy in Electronics and Communication Engineering is a record of research work carried out by Mr. Mahipal Singh under my supervision and guidance.

All help received by him/her from various sources have been duly acknowledged.

No part of this thesis has been submitted elsewhere for award of any other degree.

Date: 31 Mar 2014 Place: Tezpux

Parthepation Sales,

(Prof. P. P. Sahu) Supervisor, Professor, Department of Electronics and Communication Engineering, Tezpur University, Napaam, Tezpur, Assam, India PIN-784 028

### **TEZPUR UNIVERSITY**

This is to certify that the thesis entitled "Study of Multi-Channel Spread Spectrum Systems for Wireless Communication" submitted by Mr. Mahipal Singh to the Tezpur University in the Department of Electronics and Communication Engineering under the School of Engineering in partial fulfillment for the award of the degree of Doctor of Philosophy in Electronics and Communication Engineering has been examined by us and found to be satisfactory.

The committee recommends for the award of the degree of Doctor of Philosophy.

Supervisor .

External Examiner

Date:

#### Acknowledgements

I would like to take this opportunity to express my great gratitude to my supervisor Prof. P.P.Sahu for his supervision, support and encouragement throughout my research. I sincerely appreciate his invaluable help and suggestions in writing papers, thesis and helping me for my presentations. His enlighten suggestions and constructive criticize has gone a long way in the successful completion of research work including the thesis writing.

I would like to thank J.C. Dutta Professor & HoD, Dept. of Electronics & Communication Engineering, Tezpur University for his constant encouragement and timely support. His friendly personality, that has enabled me to interact freely and learn a lot from him.

I would like to thank by doctoral committee members Prof. M. Bhuyan and Dr. S. Sharma for their consistent encouragement, and support during the whole period of my research.

I would also like to thank all the teaching and non teaching members of their technical and non-technical support throughout my stay in the Dept.

My thanks to all the research scholars who have helped me in one way or another specially, Hemanga Kumar Das, Bidyut Deka, Manowar Hussain Bhuyan, Bijoy Chand Chatterjee, Awadhesh Pachauri, Aradhana Dutta, Anup Bodoloi, Pranjal Borah, Nilima, Shashikala Kalita , Special thanks to all my friends who have helped me for their advice, help and tolerance. My colleague Mr Prmod Kumar and Mr Hasin Ahmad who have helped me, guided me and provided full support for hardware implementation of the circuits and they deserve special thanks.

At last, but not the least I would like to acknowledge to my family members for providing encouragement and support during work on this thesis. Special thanks go to my wife, Kemta Singh and my daughters Monika and Manisha, without whose patience, understanding, support, and countless sacrifices, I would not have been able to make it possible.

#### **Mahipal Singh**

## Abstract

The advancement in the technology has flourished the communication sector in all directions and the concept of communication has changed from traditional wired telephone to wireless telephone. However, the resource that makes wireless communications possible is the spectrum which is scarce and limited. The growth in the number of wireless users and services has caused pressure on efficient use of available bandwidth (spectrum). To elucidate some of challenges of wireless communication the spread spectrum technique has emerged as a well-known technique. The spread spectrum based Code division multiple access (CDMA) techniques have been widely accepted for designing the next generation wireless systems with many advantages. This thesis, investigates multiplexing/multi-channeling of wireless systems using spread spectrum communication for efficient use of available spectrum by accommodating more number of users on a single channel. The proposed signal processing techniques are also studied to enhance the performance of existing systems.

Firstly, we investigate the CPSK technique for multiplexing/multi-Channing using DSSS and FHSS system. The designed and simulated systems accommodate more of number users on the same channel. The performance for BER was analyzed with a simulation model using software.

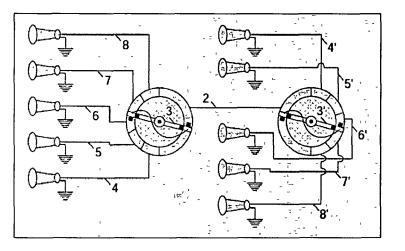

Secondly, we have proposed a binary phase shift keying (BPSK) demodulator for processing the signal in the receiver. This demodulator has been investigated for BER performance analytically and with simulation model.

Thirdly, the M-ary based CFHSS system has been designed and simulated for accommodating more users using band pass filters (BPF). The performance of the system is tested under different hop size. It shows that higher the hop size, lesser the BER and vice versa.

Lastly, we concentrate on the design of FHSS system for multi-channeling using proposed sinusoidal frequency to voltage converter (FVC) by replacing the BPF. The FVC also tested and analyzed for linearity and ripples. The FVC provides a higher frequency range of conversion with linear output.

## Contents

| Dedication                    | ii   |

|-------------------------------|------|

| Declaration                   | iii  |

| Certificate of Supervisor     | iv   |

| Certificate of Examiner       | v    |

| Acknowledgement               | vi   |

| Abstract                      | vii  |

| Table of contents             | viii |

| List of Figures               | ix   |

| List of author's publications | xii  |

#### 1 Introduction

| 1.1 | Overview                                            | 1/1 |

|-----|-----------------------------------------------------|-----|

| 1.2 | Multi-Channel Communications                        | 2/1 |

| 1.3 | Open issues in Multi-Channel Wireless Communication | 3/1 |

| 1.4 | Objectives                                          | 4/1 |

| 1.5 | Contributions                                       | 5/1 |

| 1.5 | Thesis Organization                                 | 6/1 |

#### 2 Overviews of Spread Spectrum Signaling for Wireless Communications

| 2.1 | Introdu | iction                     | 1/2 |

|-----|---------|----------------------------|-----|

| 2.2 | Pseudo  | -noise Sequences           | 1/2 |

|     | 2.2.1   | Maximum Length Sequences   | 2/2 |

|     | 2.2.2   | Gold Codes Sequences       | 3/2 |

|     | 2.2.3   | Barker Sequences           | 4/2 |

|     | 2.2.4   | Properties of PN Sequences | 5/2 |

| 2.3 | Spread  | Spectrum Technique         | 6/2 |

| 2.4 | Direct  | Sequence Spread Spectrum   | 7/2 |

|     | 2.4.1    | Basic DSSS Transmitter                         | 07/2 |

|-----|----------|------------------------------------------------|------|

|     | 2.4.2    | Processing Gain in DSSS System                 | 09/2 |

|     | 2.4.3    | Basic DSSS Receiver                            | 10/2 |

|     | 2.4.4    | Code Phase Shift Keying based DSSS Transmitter | 11/2 |

|     | 2.4.5    | Code Phase Shift Keying based DSSS Receiver    | 12/2 |

|     | 2.4.6    | Code Division Multiple Access                  | 13/2 |

| 2.5 | Frequen  | cy Hop Spread Spectrum                         | 15/2 |

|     | 2.5.1    | Basic FHSS Transmitter                         | 16/2 |

|     | 2.5.2    | Basic FHSS Receiver                            | 18/2 |

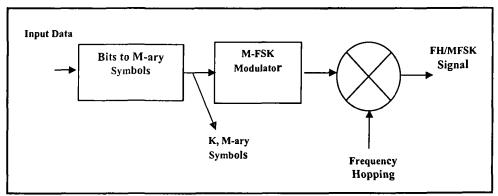

|     | 2.5.3    | M-ary FHSS Transmitter                         | 18/2 |

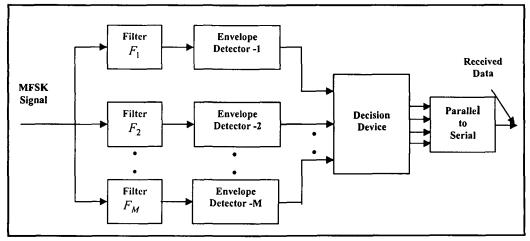

|     | 2.5.4    | M-ary FHSS Receiver                            | 19/2 |

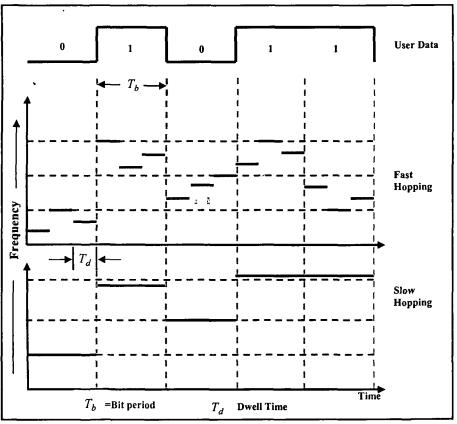

|     | 2.5.5    | Slow and Fast FHSS System                      | 20/2 |

|     | 2.5.6    | Comparison between DSSS and FHSS               | 22/2 |

| 2.6 | Noise in | Communication Systems                          | 22/2 |

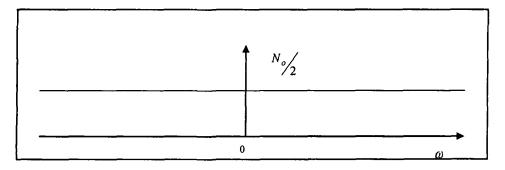

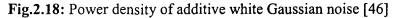

|     | 2.6.1    | Additive White Gaussian Noise                  | 24/2 |

|     | 2.6.2    | Jamming Noise                                  | 25/2 |

|     | 2.6.3    | Jamming to Signal Ratio                        | 25/2 |

| 2.7 | Bit Erro | r Rate                                         | 26/2 |

| 2.8 | Conclus  | ion                                            | 28/2 |

# **3** Review of Multiplexing and Multiple Access Techniques and their Evaluation for Wireless Communications

| 3.1 | Introdu | action                                                 | 01/3 |

|-----|---------|--------------------------------------------------------|------|

| 3.2 | Multip  | lexing                                                 | 01/3 |

|     | 3.2.1   | Time Division Multiplexing and Time Division           |      |

|     |         | Multiple Acceses                                       | 02/3 |

|     | 3.2.2   | Frequency Division Multiplexing and Frequency Division | on   |

|     |         | Multiple Access                                        | 07/3 |

|     | 3.2.3   | Code Division Multiplexing and Code Division           |      |

|     |         | Multiple Access                                        | 10/3 |

|     | 3.2.4   | Space Multiplexing and Space Division Multiple |      |

|-----|---------|------------------------------------------------|------|

|     |         | Access                                         | 17/3 |

|     | 3.2.5   | Comparison analysis TDM, FDM, CDM, SDM         | 21/3 |

| 3.3 | Binary  | Phase Shift Keying Demodulator                 | 24/3 |

| 3.4 | Sinusoi | dal Frequency to Voltage Converter             | 26/3 |

| 3.5 | Growth  | of Wireless Users                              | 28/3 |

| 3.6 | Conclu  | sion                                           | 30/3 |

|     |         |                                                |      |

#### 4 Design and Simulation of CPSK based Multi-Channel Direct Sequence Spread Spectrum

| 4.1 | Introduc | ction                                              | 01/4  |

|-----|----------|----------------------------------------------------|-------|

| 4.2 | Archite  | cture of Proposed CPSK based Multi- Channel DSSS   |       |

|     | System.  |                                                    | 01/4  |

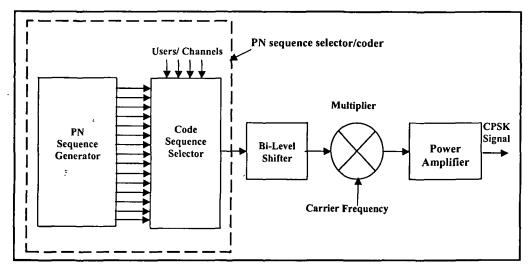

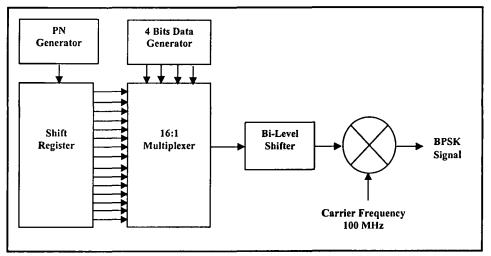

|     | 4.2.1    | CPSK based DSSS Transmitter                        | 02/4/ |

|     | 4.2.2    | CPSK based DSSS Receiver                           | 03/4  |

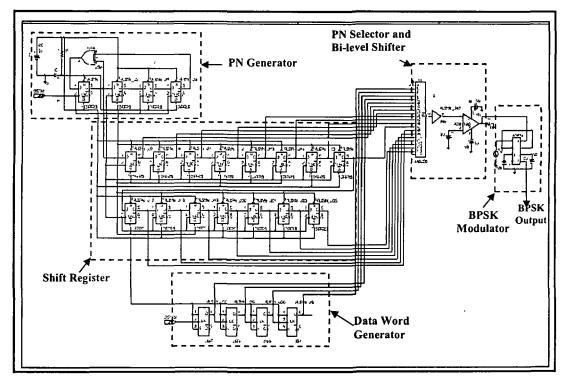

| 4.3 | CPSK E   | Based DSSS Transmitter Design                      | 04/4  |

|     | 4.3.1    | Pseudorandom Noise Sequence Generator              | 04/4  |

|     | 4.3.2    | Shift Register                                     | 08/4  |

|     | 4.3.3    | Data Word Generator                                | 10/4  |

|     | 4.3.4    | PN Sequence Selector and Bi-level Shifter          | 12/4  |

|     | 4.3.5    | BPSK Modulator                                     | 15/4  |

| 4.4 | Simulat  | ion Results of CPSK based DSSS Transmitter         | 18/4  |

| 4.5 | CPSK b   | ased DSSS Receiver Design                          | 22/4  |

|     | 4.5.1    | BPSK Demodulator                                   | 23/4  |

|     | 4.5.2    | Filtering and Decision Device                      | 24/4  |

|     | 4.5.3    | Correlator Circuit                                 | 27/4  |

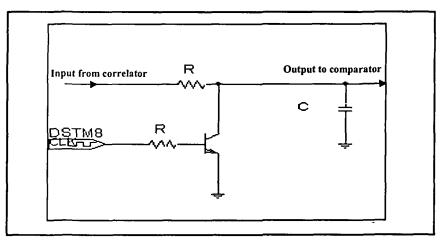

|     | 4.5.4    | Integrate and Dump                                 | 28/4  |

|     | 4.5.5    | Select Largest Logic                               | 30/4  |

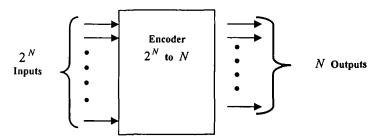

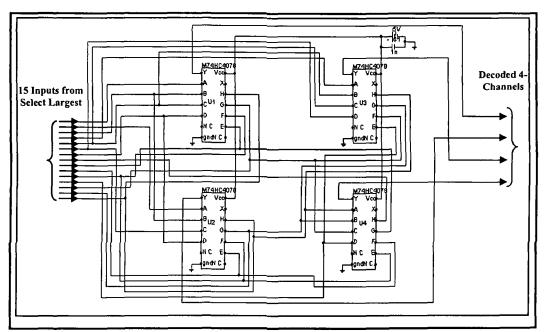

|     | 4.5.6    | Decoder                                            | 32/4  |

| 4.6 | Simulat  | ion Results of CPSK Receiver with BPSK Demodulator | 34/4  |

|   | 4.7  | Receive  | r Design with Proposed BPSK to ASK converter and                                               |        |

|---|------|----------|------------------------------------------------------------------------------------------------|--------|

|   |      | Peak De  | etector                                                                                        | 39/4   |

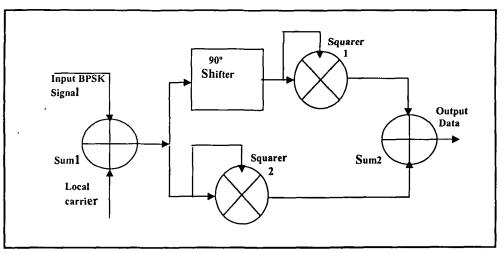

|   |      | 4.7.1    | Adder 1                                                                                        | 41/4   |

|   |      | 4.7.2    | 90° Phase Shifter                                                                              | 43/4   |

|   |      | 4.7.3    | Squaring Circuits                                                                              | 44/4   |

|   |      | 4.7.4    | Adder 2                                                                                        | 44/4   |

|   | 4.8  | Simulati | ion Results of CPSK Receiver with Proposed BPSK to ASK                                         |        |

|   |      | Convert  | er and Peak Detector                                                                           | 46/4   |

|   | 4.9  | Conclus  | ion                                                                                            | 51/4   |

| 5 | Perf | formance | Evaluation of CPSK based DSSS System                                                           |        |

|   | 5.1  | Introduc | tion                                                                                           | 01/5   |

|   | 5.2  | Analytic | al Performance Evaluation                                                                      | 01/5   |

|   |      | 5.2.1    | Performance under AWGN                                                                         | 01/5   |

|   |      | 5.2.2    | Performance under AWGN with Continuous Wave                                                    |        |

|   |      |          | Jamming                                                                                        | 03/5   |

|   |      | 5.2.3    | Performance with Phase Mismatch                                                                | 06/5   |

|   | 5.3  | Perform  | ance Evaluation with Simulation Setup                                                          | 08/5   |

|   |      | 5.3.1    | Bit Error Rate Measurement                                                                     | 11/5   |

|   |      | 5.3.2    | Jamming Performance from Simulation Model                                                      | 12/5   |

|   | 5.4  | Perform  | ance of Proposed BPSK Demodulator                                                              | 13/5   |

|   | 5.5  | Phase ar | nd Amplitude margin with Simulation Model                                                      | 15/5   |

|   | 5.6  | Perform  | ance measurement with Eye Pattern                                                              | 17/5   |

|   | 5.7  | Experim  | ental performance Measurement                                                                  | 19/5   |

|   | 5.8  | Conclus  | ion                                                                                            | . 20/5 |

| 6 | Spre |          | imulation of Multi-Channel Frequency Hopping<br>rum Communication System using M-ary Frequency |        |

|   | 6.1  | Introduc | tion                                                                                           | 01/6   |

|   | 6.2  | Archited | ture of Proposed CMFSK based Multi-Channel Frequency                                           |        |

|   |      | Hopped   | Spread Spectrum System                                                                         | 01/6   |

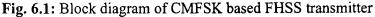

|   |      | 6.2.1  | · CMFSK based FHSS Transmitter                          | 02/ |

|---|------|--------|---------------------------------------------------------|-----|

|   |      | 6.2.2  | CMFSK based FHSS Receiver                               | 03/ |

|   | 6.3  | CMFS   | SK based FHSS Transmitter Design                        | 03/ |

|   |      | 6.3.1  | Serial In Parallel Out                                  | 05/ |

|   |      | 6.3.2  | Digital to Analog Converter                             | 06/ |

|   |      | 6.3.3  | Voltage Control Oscillator                              | 08/ |

|   | 6.4  | Simul  | ation Results of CMFSK based FHSS Transmitter           | 12/ |

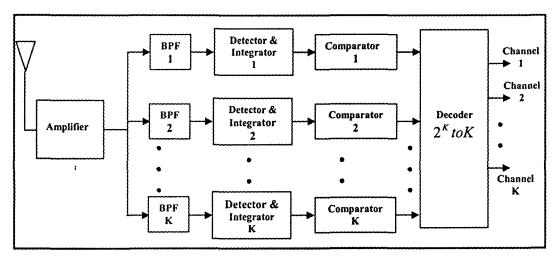

|   | 6.5  | CMFS   | SK based FHSS Receiver Design with Band Pass Filters    | 16/ |

|   |      | 6.5.1  | Band Pass Filters                                       | 16/ |

|   |      | 6.5.2  | Detector and Integrator                                 | 20/ |

|   |      | 6.5.3  | Dump and Comparator                                     | 21/ |

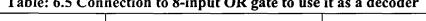

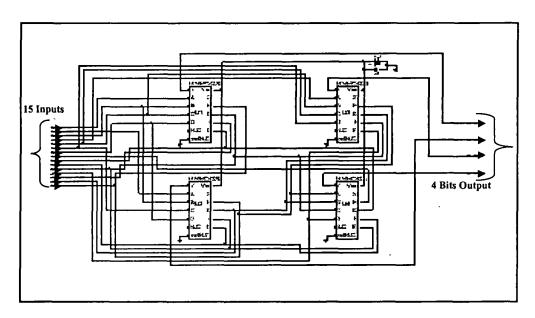

|   |      | 6.5.4  | Decoder                                                 | 22  |

|   | 6.6  | Simul  | ation Results of Band Pass Filters based CMFSK Receiver | 24/ |

|   | 6.7  | CMFS   | SK based Receiver Design with Frequency to Voltage      |     |

|   |      | Conve  | erter                                                   | 28/ |

|   |      | 6.7.1  | Frequency to Voltage Converter Principle                | 28/ |

|   |      |        | 6.7.1.1 Linearization of FVC                            | 31/ |

|   |      |        | 6.7.1.2 Ripple Calculation                              | 32/ |

|   |      |        | 6.7.1.3 Response Time                                   | 35/ |

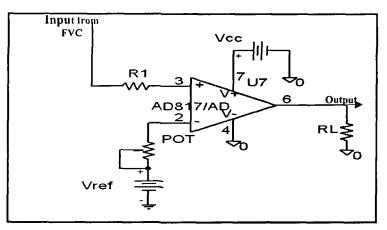

|   |      | 6.7.2  | Comparators                                             | 37/ |

|   |      | 6.7.3  | Priority Decoder                                        | 39/ |

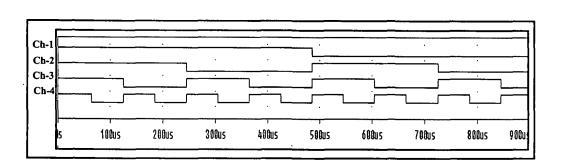

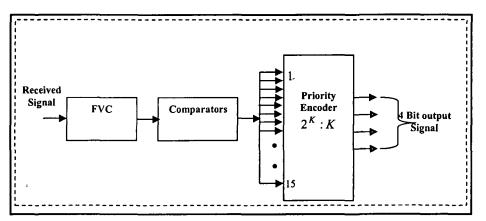

|   | 6.8  | Simul  | ation Results of FVC based CMFSK Receiver               | 41/ |

|   | 6.9  | Concl  | usion                                                   | 45/ |

| 7 | Peri | forman | ce Evaluation of CMFSK based FHSS System                |     |

|   | 7.1  | Introd | uction                                                  | 01/ |

|   | 7.2  | Analy  | tical Performance of CMFSK based FHSS System            | 01/ |

|   |      | 7.2.1  | Symbol Error Rate under AWGN                            | 02/ |

|   |      | 7.2.2  | Bit Error Rate obtained from Symbol Error Rate          | 03/ |

|   | 7.3  | SER f  | rom Simulation Model                                    | 04/ |

|   |      | 7.3.1  | Bit Error Rate                                          | 07/ |

.

|   | 7.4 | Performance of Code M-ary CMFSK based FHSS with proposed |      |

|---|-----|----------------------------------------------------------|------|

|   |     | Frequency to Voltage Converter                           | 11/7 |

|   |     | 7.4.1 Analytical model for BER under AWGN                | 11/7 |

|   |     | 7.4.2 Bit Error Rate from Measurement                    | 11/7 |

|   | 7.5 | Performance measurement with Eye Pattern                 | 13/7 |

|   | 7.6 | Comparison of proposed DSSS and FHSS under Jamming       | 14/7 |

|   | 7.7 | Performance Measurement Experimentally                   | 15/7 |

|   | 7.8 | Conclusion                                               | 17/7 |

| 8 | Con | clusion and Future Scope                                 |      |

|   | 8.1 | Conclusions                                              | 01/8 |

|   | 8.2 | Future Scope                                             | 03/8 |

### List of Tables

| Table No           | Table Name                                               | Page No |

|--------------------|----------------------------------------------------------|---------|

| <u>Chapter – 2</u> |                                                          |         |

| Table-2.1          | Different Barker Codes                                   | 04/2    |

| Table-2.2          | Comparison between DSSS and FHSS                         | 22/2    |

| <u>Chapter – 3</u> |                                                          |         |

| Table-3.1          | Performance comparison of multiplexing techniques        | 21/3    |

| Table-3 .2         | Previous works on Multiple-excess techniques             | 22/3    |

| Table-3.1          | Comparison of different FVC                              | 28/3    |

| <u>Chapter – 4</u> |                                                          |         |

| Table-4.1          | Output of PN sequence generator                          | 08/4    |

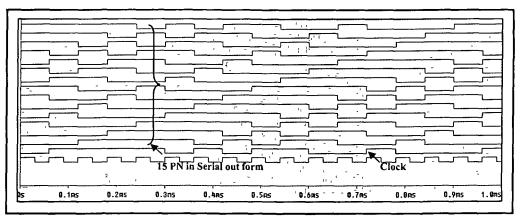

| Table-4 .2         | 15 PN sequences obtained from shift registers            | 09/4    |

| Table-4.3          | List of components with specification                    | 19/4    |

| Table-4 .4         | Truth table of decoder                                   | 32/4    |

| Table-4 .5         | 8 Input OR gate as a 16 to 4 Decoder                     | 33/4    |

| Table-4 .6         | List of components used for DSSS receiver design         | 35/4    |

| Table-4 .7         | Simulated Component list for proposed DSSS Receiver      | 46/4    |

| <u>Chapter – 6</u> |                                                          |         |

| Table-6.1          | Control voltage of MAX 038                               | 09/6    |

| Table-6 .2         | VCO Output Frequencies                                   | 12/6    |

| Table-6.3          | List of components used for design of transmitter        | 13/6    |

| Table-6 .4         | Components values for BPF design                         | 19/6    |

| Table-6.5          | Connection to 8 input OR gate to use as Decoder          | 23/6    |

| Table-6 .6         | List of components used in CMFHSS receiver               | 24/6    |

| Table-6.7          | Truth Table, for 16 to 4 decoder Priority Decoder        | 39/6    |

| Table-6.8          | Truth table of HCF 4532B                                 | 40/6    |

| Table-6.9          | List of components used for FVC Based<br>CMFHSS Receiver | 43/6    |

### List of Figures

| Figure Name Pa                                            | ge No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

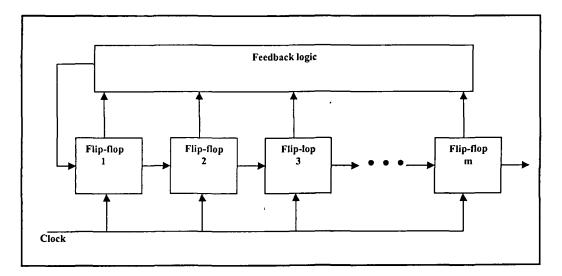

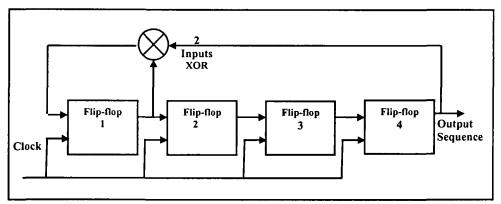

| Block diagram of feedback shift register                  | 03/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

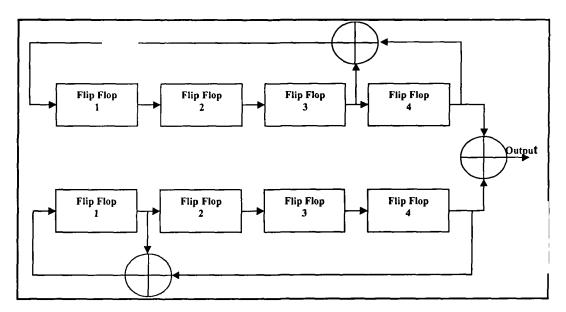

| Generation of Gold code by combining two m-codes          | 03/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

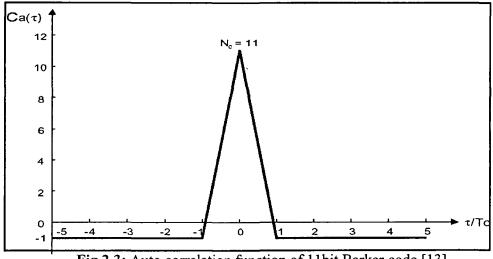

| Auto correlation function of 11bit Barker code            | 05/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

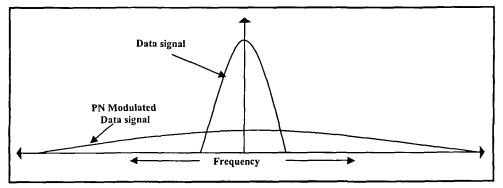

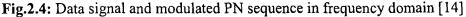

| Data signal and modulated PN sequence in frequency domain | n 06/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

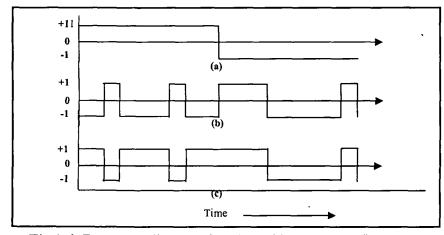

| Block diagram of basic DSSS transmitter                   | 08/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

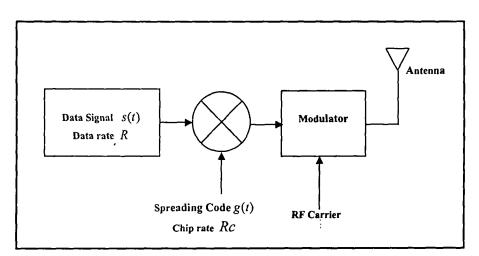

| Data spreading in DSSS                                    | 09/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

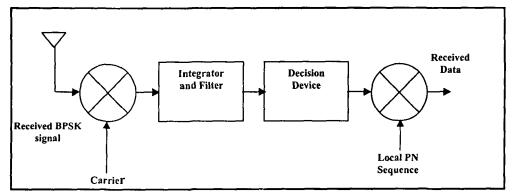

| Block diagram of DSSS receiver                            | 10/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data despreading in DSSS                                  | 11/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

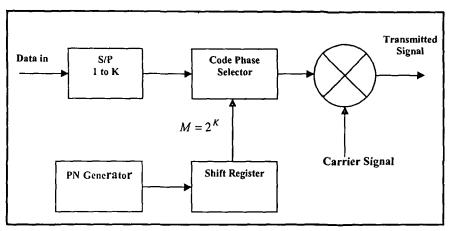

| Block diagram of CPSK transmitter                         | 12/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

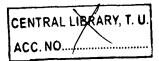

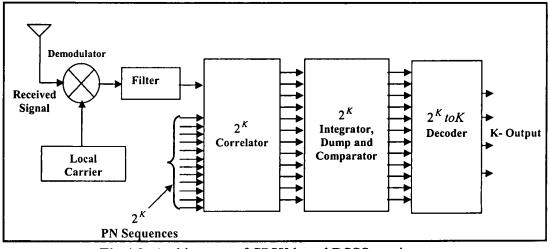

| Block diagram of CPSK receiver                            | 13/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

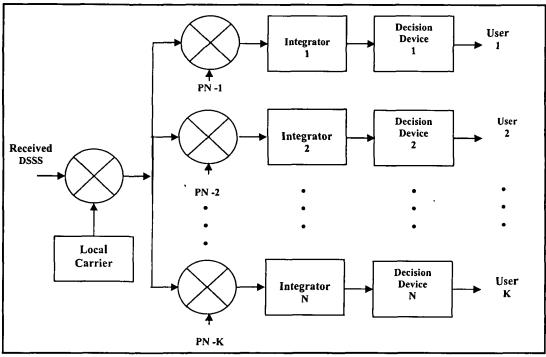

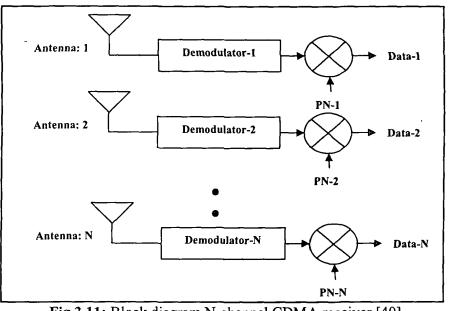

| Block diagram of CDMA receiver system                     | 15/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

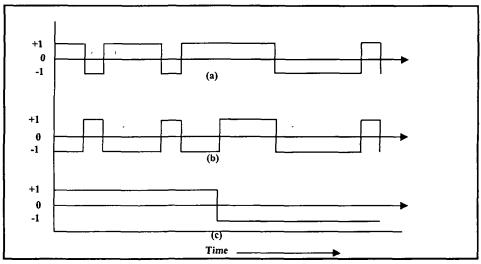

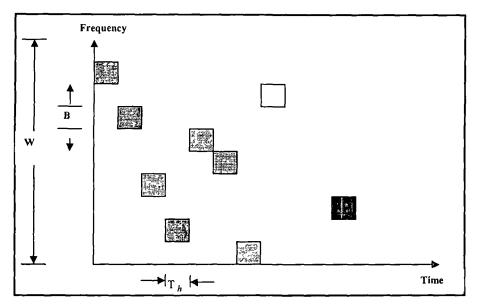

| Basic concept of frequency hopping spread spectrum        | 16/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

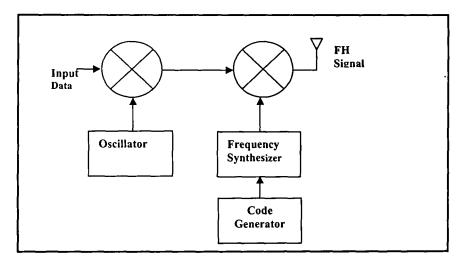

| Block diagram of FHSS transmitter                         | 17/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

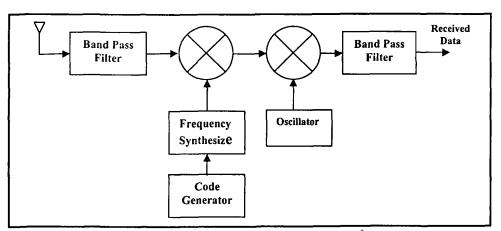

| Block diagram FHSS receiver                               | 18/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| M-FSK spread spectrum transmitter                         | 19/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MFSK Spread Spectrum receiver                             | 20/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Time and hop relation in slow/fast hopping                | 21/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Power density of additive white Gaussian noise            | 24/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BER Performance of a BPSK system under AWGN               | 27/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                           | Block diagram of feedback shift register<br>Generation of Gold code by combining two m-codes<br>Auto correlation function of 11bit Barker code<br>Data signal and modulated PN sequence in frequency domain<br>Block diagram of basic DSSS transmitter<br>Data spreading in DSSS<br>Block diagram of DSSS receiver<br>Data despreading in DSSS<br>Block diagram of CPSK transmitter<br>Block diagram of CPSK receiver<br>Block diagram of CDMA receiver system<br>Basic concept of frequency hopping spread spectrum<br>Block diagram of FHSS transmitter<br>Block diagram FHSS receiver<br>M-FSK spread spectrum transmitter<br>MFSK Spread Spectrum receiver<br>Time and hop relation in slow/fast hopping<br>Power density of additive white Gaussian noise |

#### <u>Chapter – 3</u>

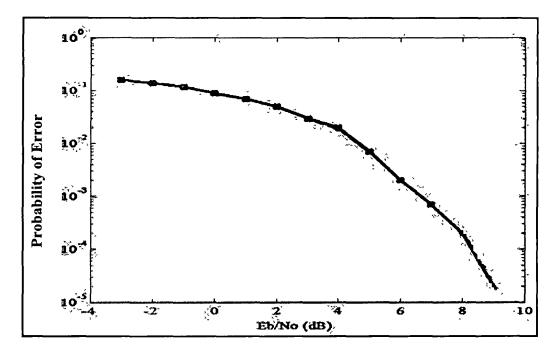

| Fig-3.1 Principle of multiplexing                    |                                  | 02/3 |

|------------------------------------------------------|----------------------------------|------|

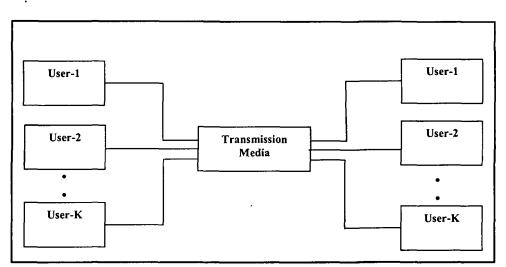

| Fig-3.2 Block diagram of commutator based TDM system |                                  | 03/3 |

| Fig-3.3 Pattern distributor (Sampling machine)       |                                  | 04/3 |

| Fig-3.4                                              | Principle of TDMA                | 05/3 |

| Fig-3.5                                              | Bell's harmonic telegraph system | 07/3 |

| Fig-3.6                                              | N2 Carrier system for FDM        | 08/3 |

| Fig-3.7  | Principle of FDMA                              | 09/3 |

|----------|------------------------------------------------|------|

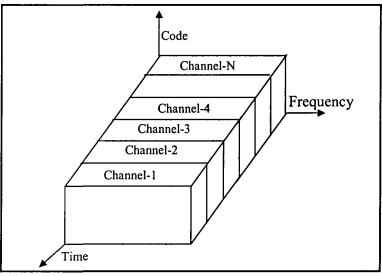

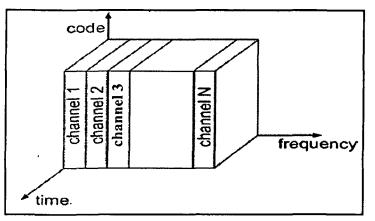

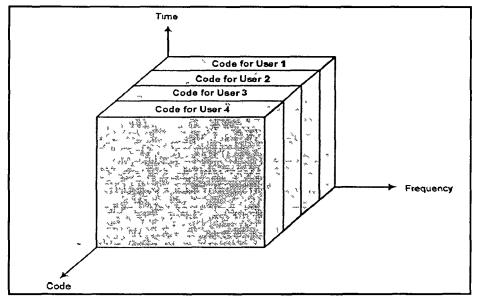

| Fig-3.8  | Concept of CDMA                                | 11/3 |

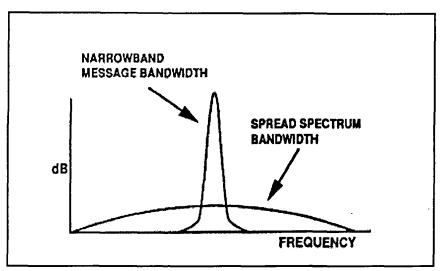

| Fig-3.9  | Bandwidth of signal before and after spreading | 12/3 |

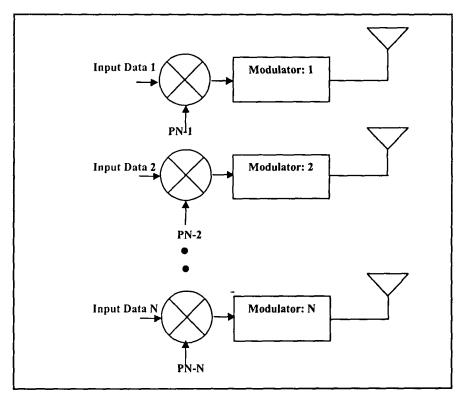

| Fig-3.10 | Block diagram of N-Channel CDMA transmitter    | 13/3 |

| Fig-3.11 | Block diagram of N-Channel CDMA receiver       | 14/3 |

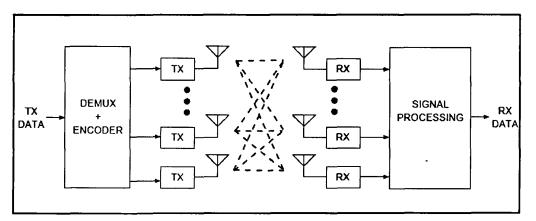

| Fig-3.12 | Block diagram or SDMA System                   | 17/3 |

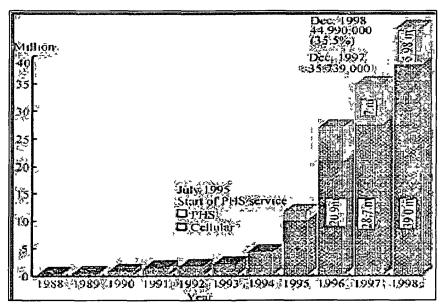

| Fig-3.13 | Growth of mobile users in Japan                | 29/3 |

#### <u>Chapter – 4</u>

| Fig-4.1 Architecture of CPSK based DSSS transmitter            |                                                            | 02/4 |

|----------------------------------------------------------------|------------------------------------------------------------|------|

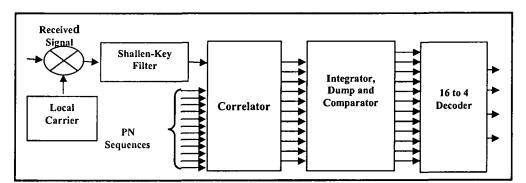

| Fig-4.2 Architecture of CPSK based Multi-Channel DSSS receiver |                                                            | 03/4 |

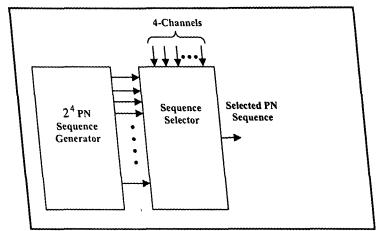

| Fig-4.3                                                        | Fig-4.3 Block diagram of LFSR PN sequence generator        |      |

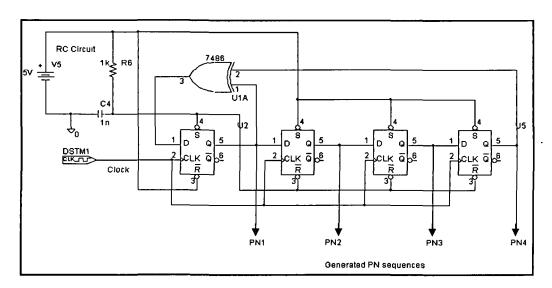

| Fig-4.4                                                        | Fig-4.4 Simulated circuit diagram of PN sequence generator |      |

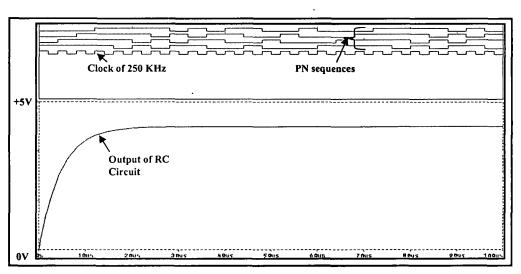

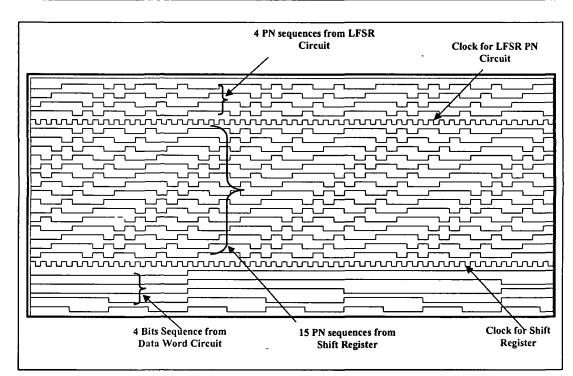

| Fig-4.5                                                        | Simulated Output of PN sequence generator                  | 07/4 |

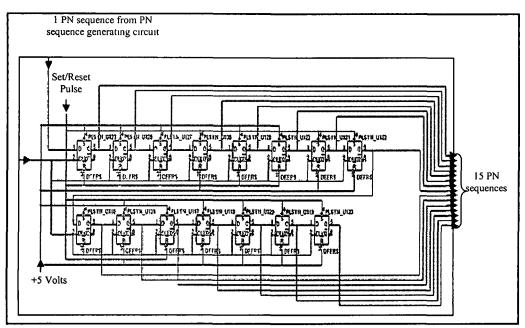

| Fig-4.6                                                        | Simulated circuit diagram of shift register                | 10/4 |

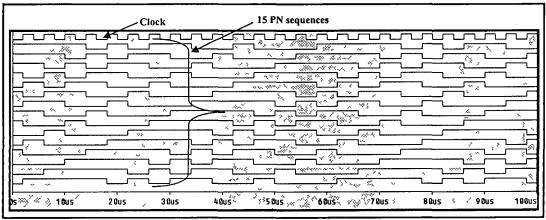

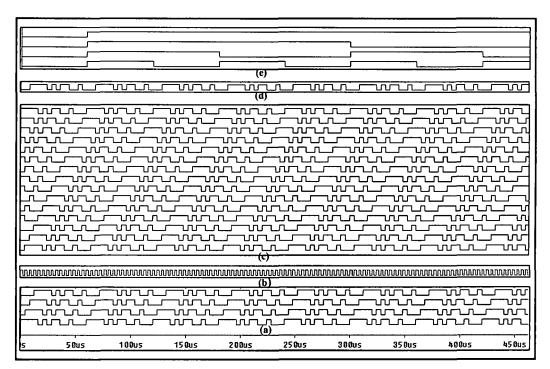

| Fig-4.7                                                        | Simulated 15 PN sequences by shift register                | 10/4 |

| Fig-4.8                                                        | Block diagram of data word generator                       | 11/4 |

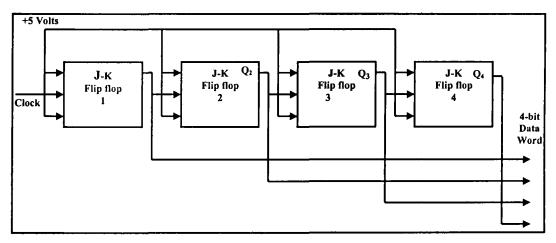

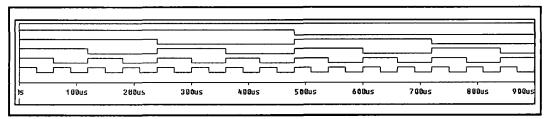

| Fig-4.9                                                        | Simulated waveforms of data word generator                 | 11/4 |

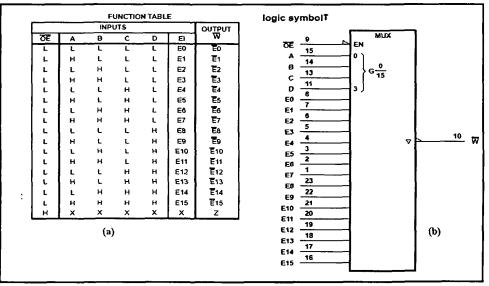

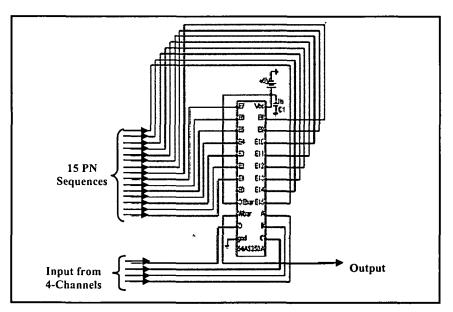

| Fig-4.10 Multiplexer 16 to 4 IC 74 as 250                      |                                                            | 12/4 |

| Fig- 4.11 Pin diagram of data selector                         |                                                            | 13/4 |

| Fig- 4.12 Simulated input and output signals of data selector  |                                                            | 13/4 |

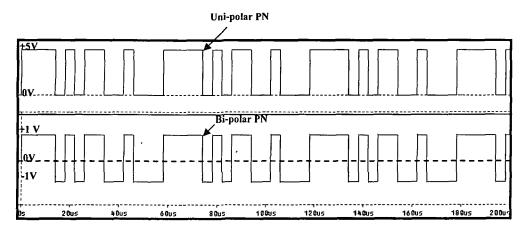

| Fig- 4.13 Simulated Bi-level circuit diagram                   |                                                            | 14/4 |

| Fig- 4.14                                                      | Input and Output of Bi-level Shifter                       | 14/4 |

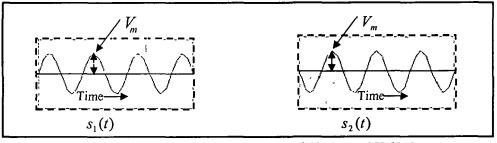

| Fig- 4.15                                                      | Representation of '1' and '0' in BPSK                      | 15/4 |

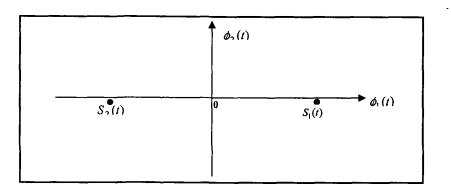

| Fig- 4.16                                                      | BPSK signal constellation                                  | 16/4 |

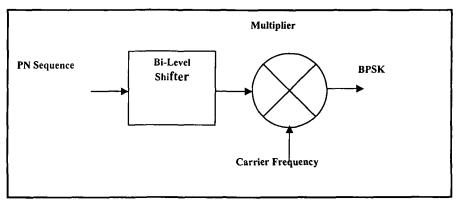

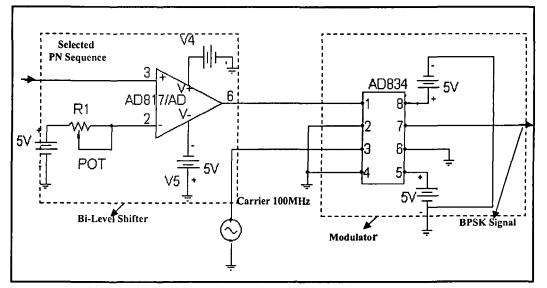

| Fig- 4.17                                                      | Block diagram of modulator                                 | 16/4 |

| Fig- 4.18                                                      | Simulated Circuit diagram of BPSK modulator                | 17/4 |

| Fig- 4.19                                                      | Input/ Out signal of modulator circuit                     | 18/4 |

| Fig- 4.20                                                      | Simulated block diagram of CPSK based DSSS Transmitter     | 19/4 |

| Fig- 4.21 | Simulated Circuit Diagram of CPSK based 4- channel DSSS        |      |

|-----------|----------------------------------------------------------------|------|

|           | transmitter                                                    | 20/4 |

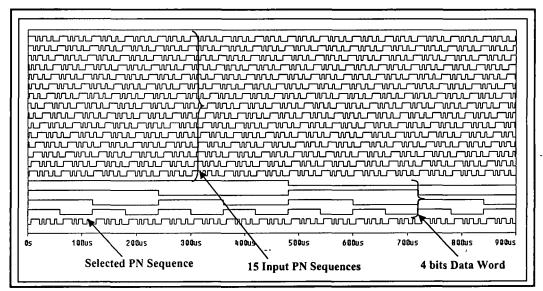

| Fig- 4.22 | Simulated outputs from PN generator, shift register and data   |      |

|           | word circuit                                                   | 21/4 |

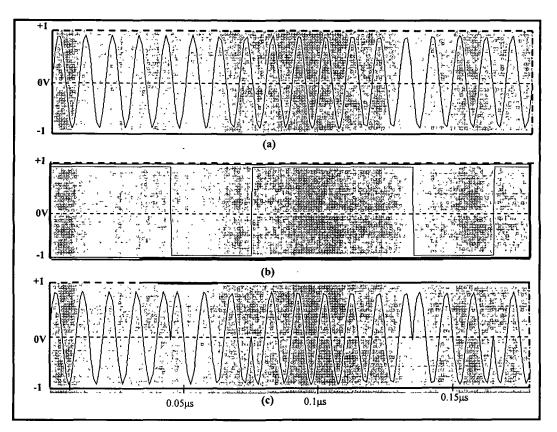

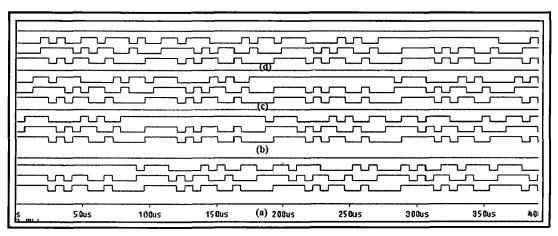

| Fig- 4.23 | Simulated waveforms of the CPSK-DSSS transmitter               | 22/4 |

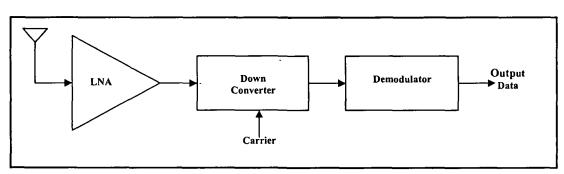

| Fig- 4.24 | Block diagram of a simple wireless receiver                    | 23/4 |

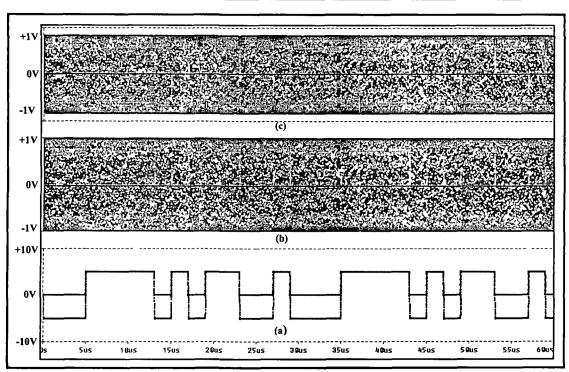

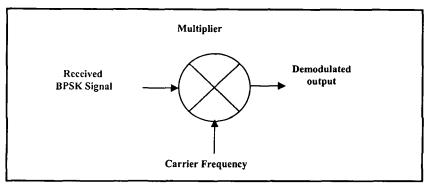

| Fig- 4.25 | Block diagram of demodulator                                   | 24/4 |

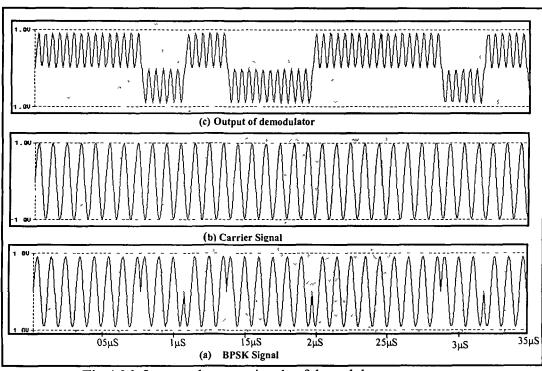

| Fig- 4.26 | Input and output signals of demodulator stage                  | 24/4 |

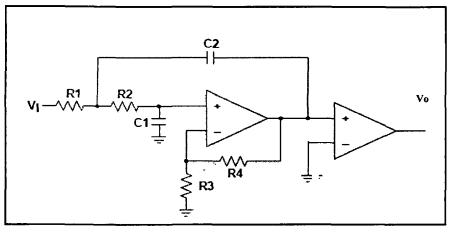

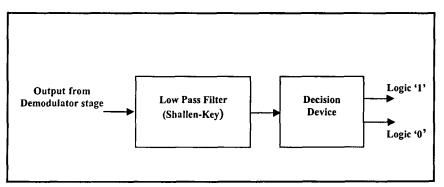

| Fig- 4.27 | Sallen-Key Low Pass filter and decision Device                 | 25/4 |

| Fig- 4.28 | Block diagram of demodulator and filter                        | 26/4 |

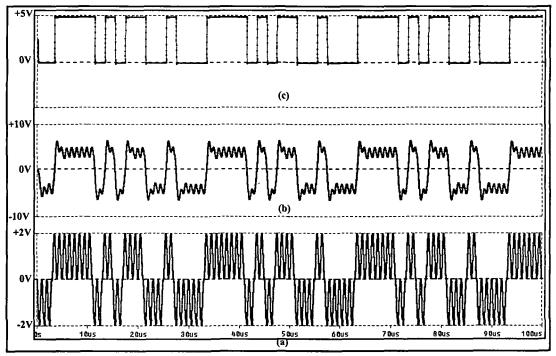

| Fig- 4.29 | Input and out waveforms of demodulator and filter              | 27/4 |

| Fig- 4.30 | Simulated waveform of correlator                               | 28/4 |

| Fig- 4.31 | Simulated circuit diagram of integrate and dump                | 29/4 |

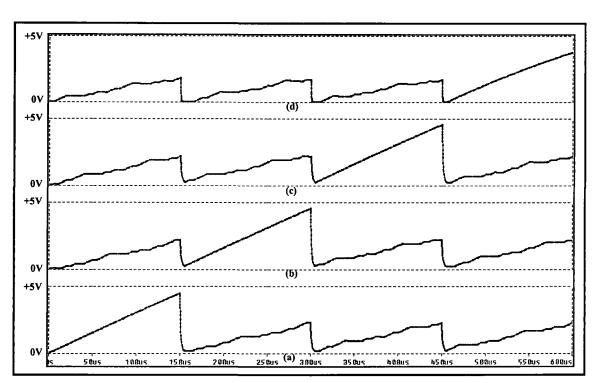

| Fig- 4.32 | Simulated waveform of integrate and dump circuit               | 30/4 |

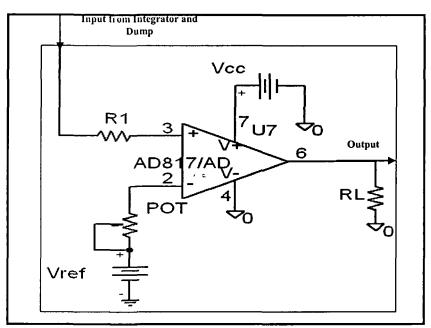

| Fig- 4.33 | Simulated circuit diagram for comparator                       | 31/4 |

| Fig- 4.34 | Simulated input/output waveform of comparator                  | 31/4 |

| Fig- 4.35 | Block diagram of decoder                                       | 33/4 |

| Fig- 4.36 | Circuit diagram of decoder                                     | 34/4 |

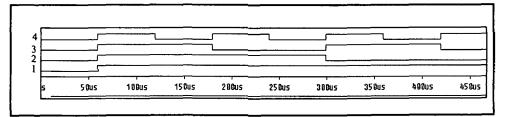

| Fig- 4.37 | Decoder output as 4-decoded channels                           | 34/4 |

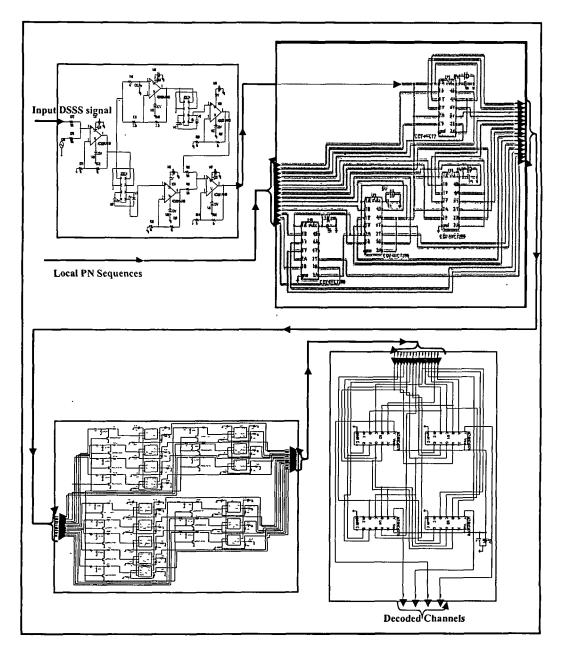

| Fig- 4.38 | P-Spice simulated block diagram of DSSS receiver               | 35/4 |

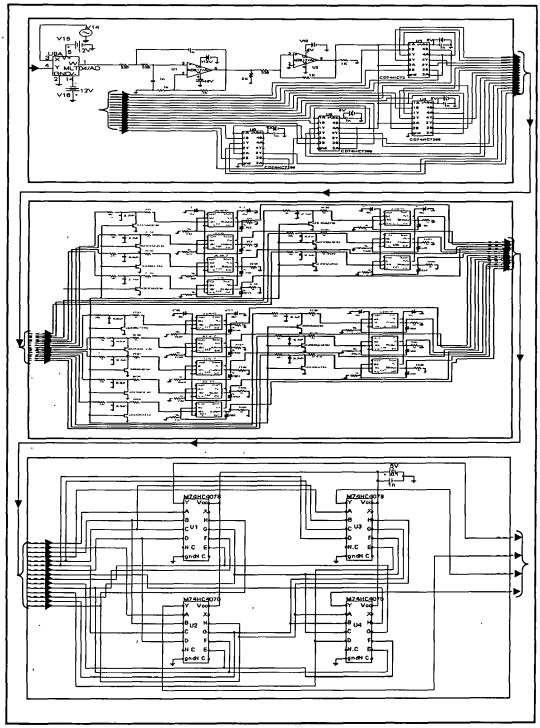

| Fig- 4.39 | P-Spice simulated circuit diagram of DSSS receiver             | 36/4 |

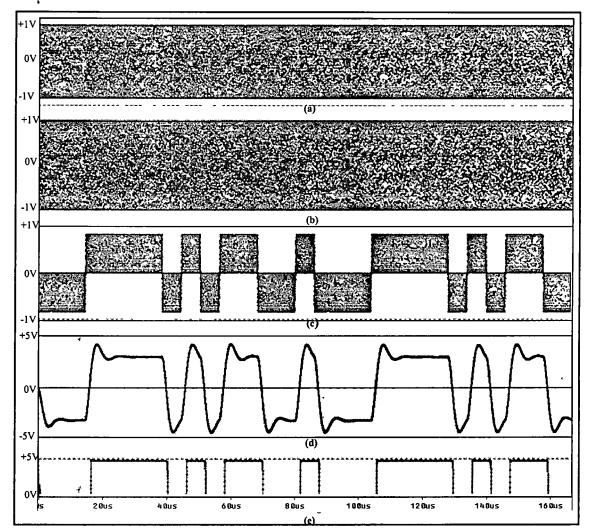

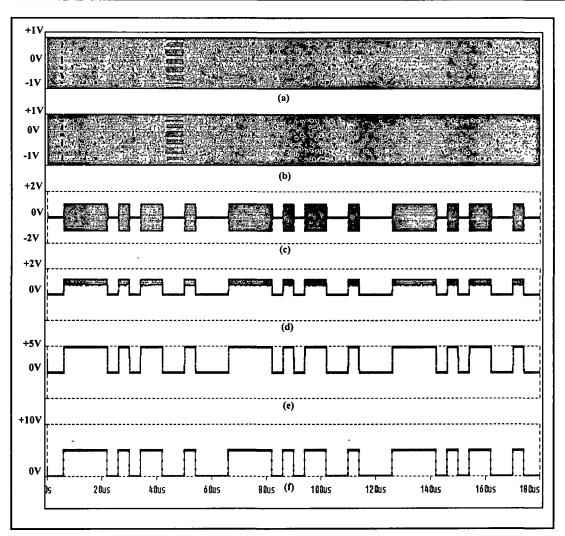

| Fig- 4.40 | P-Spice Simulated waveform of DSSS receiver at 100 MHz         | 37/4 |

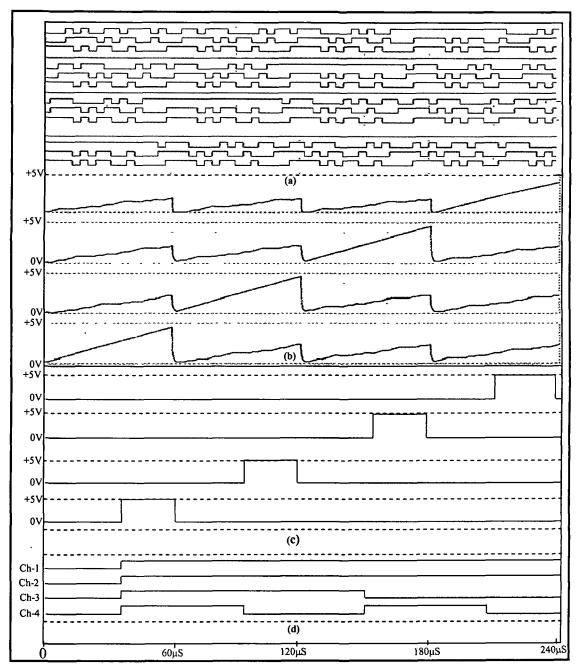

| Fig- 4.41 | P-Spice simulated waveform of the receiver at different stages | 38/4 |

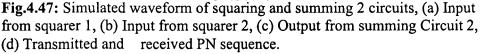

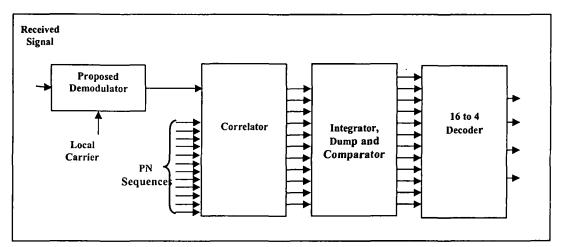

| Fig- 4.42 | Block diagram of proposed BPSK demodulator                     | 40/4 |

| Fig- 4.43 | Simulated Circuit diagram of adder1                            | 42/4 |

| Fig- 4.44 | Simulated waveforms of adder 1                                 | 42/4 |

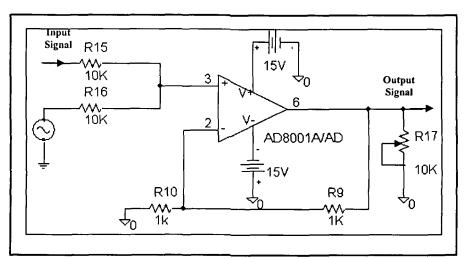

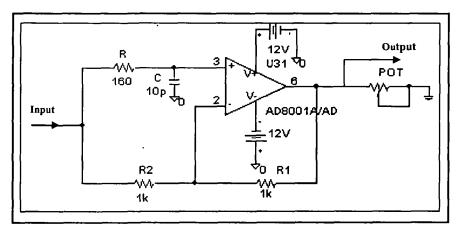

| Fig- 4.45 | Simulated circuit diagram of all pass filter                   | 43/4 |

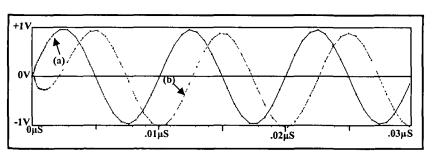

| Fig- 4.46 | Simulated waveforms all pass filter                            | 44/4 |

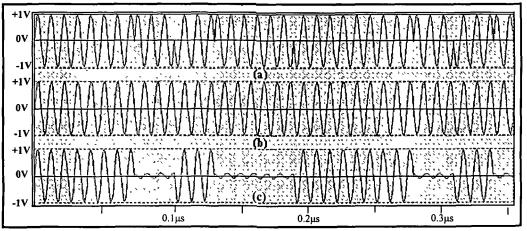

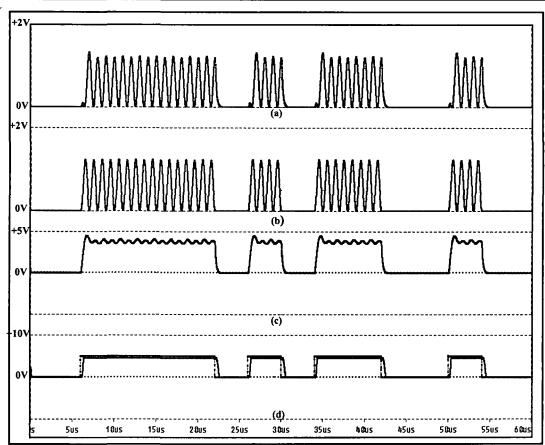

| Fig- 4.47 | Simulated waveform of squaring and summing 2 circuits          | 45/4 |

| Fig- 4.48 | Simulated block diagram of DSSS receiver                       | 47/4 |

|           |                                                                |      |

| Fig- 4.49 | Simulated circuit diagram of Proposed BPSK demodulator based DSSS receiver circuit diagram | 48/4 |

|-----------|--------------------------------------------------------------------------------------------|------|

| Fig- 4.50 | Simulated waveforms of proposed demodulator at different stages                            | 49/4 |

| Fig- 4.51 | Simulated waveforms of receiver at different stage                                         | 50/4 |

#### <u>Chapter – 5</u>

| Fig- 5.1                                                         | Fig- 5.1 Analytical performance of BPSK System and DSSS system 0. |      |

|------------------------------------------------------------------|-------------------------------------------------------------------|------|

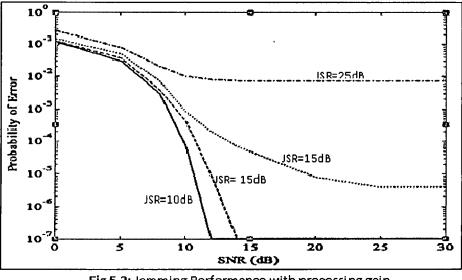

| Fig- 5.2Jamming Performance with processing gain0                |                                                                   | 06/5 |

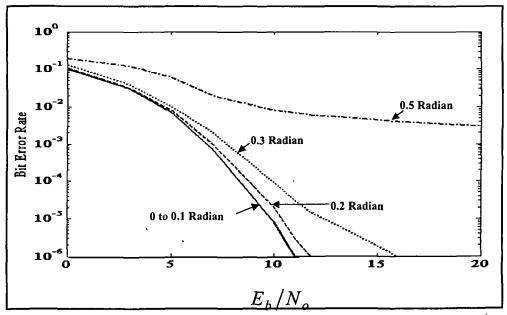

| Fig- 5.3                                                         | BER degradation due to phase mismatch                             | 07/5 |

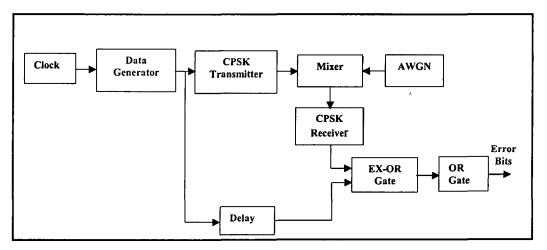

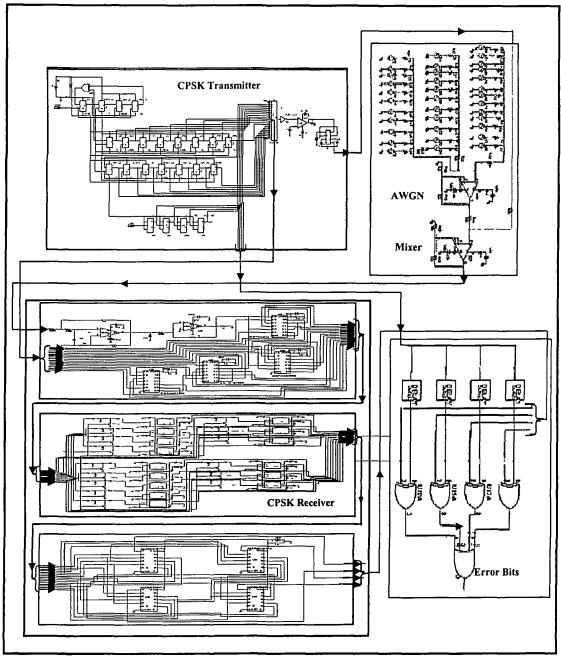

| Fig- 5.4                                                         | Simulation model for SER/BER estimation                           | 09/5 |

| Fig- 5.5                                                         | P-Spice simulated circuit diagram for SER estimation              | 10/5 |

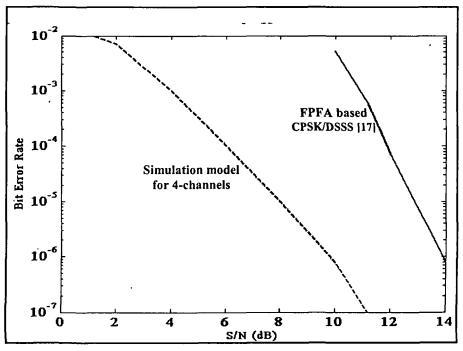

| Fig- 5.6                                                         | Comparisons of BER performances between CPSK/DSSS using           |      |

|                                                                  | simulation model and with the FPGA based CPSK /DSSS               | 11/5 |

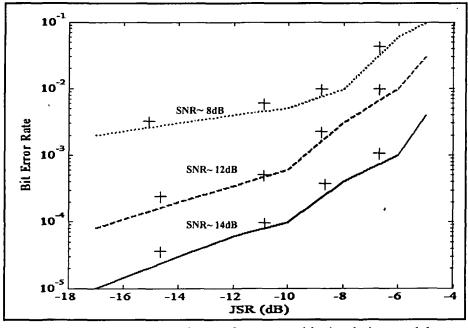

| Fig- 5.7                                                         | Jamming performance with simulation model                         | 12/5 |

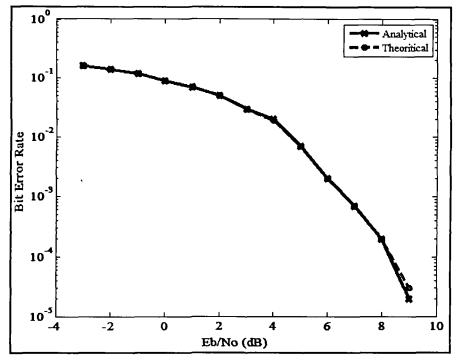

| Fig- 5.8Analytical performance of BPSK system15                  |                                                                   | 15/5 |

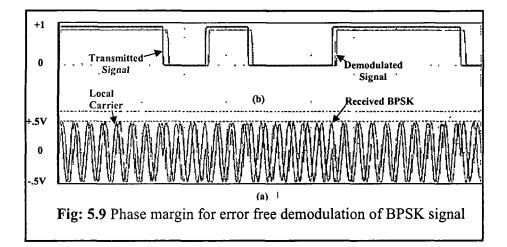

| Fig- 5.9Phase margin for error free demodulation of BPSK signal1 |                                                                   | 16/5 |

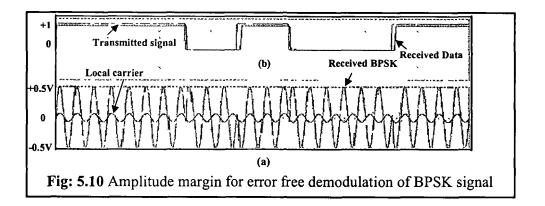

| Fig- 5.10                                                        | Amplitude margin for error free demodulation of BPSK signal       | 17/5 |

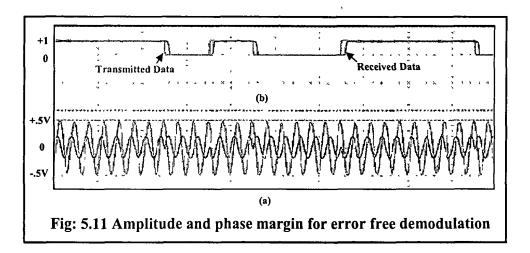

| Fig- 5.11                                                        | Amplitude and phase margin for error free demodulation            | 17/5 |

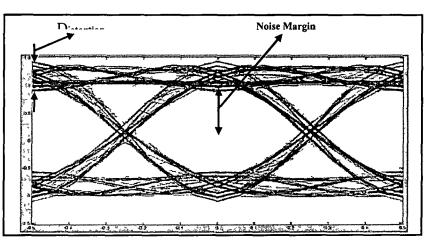

| Fig- 5.12                                                        | Eye pattern of received data at 10dB SNR                          | 18/5 |

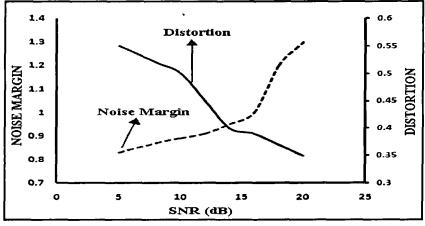

| Fig- 5.13                                                        | Plots for noise and distortion from eye diagram                   | 18/5 |

| Fig- 5.14                                                        | Experimental setup for CPSK based DSSS system                     | 19/5 |

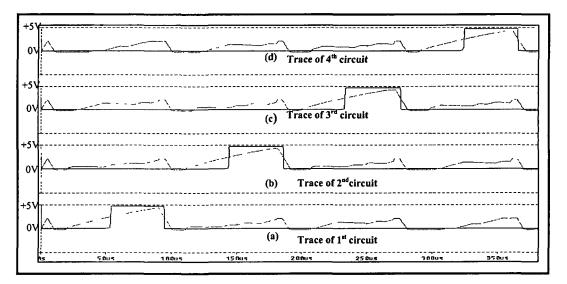

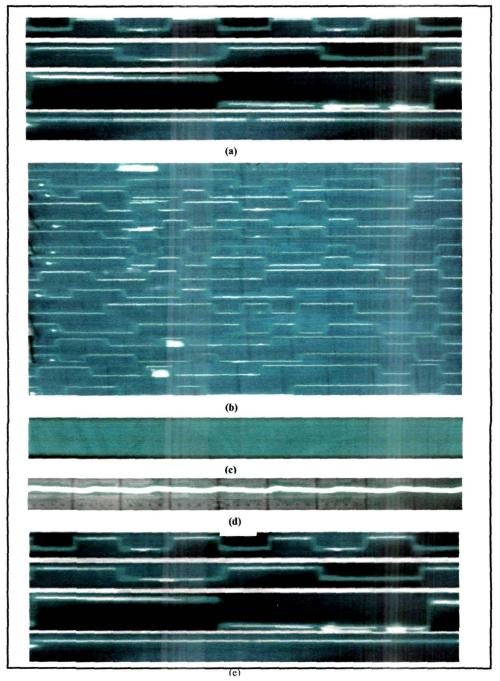

| Fig- 5.15                                                        | Experimental results                                              | 20/5 |

|                                                                  |                                                                   |      |

#### <u>Chapter – 6</u>

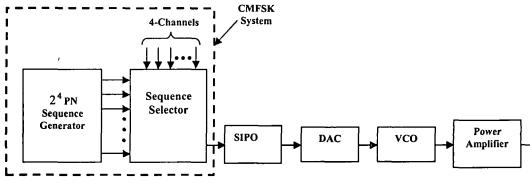

| Fig- 6.1 Block diagram of CMFSK based FHSS transmitter |                                             | 02/6 |

|--------------------------------------------------------|---------------------------------------------|------|

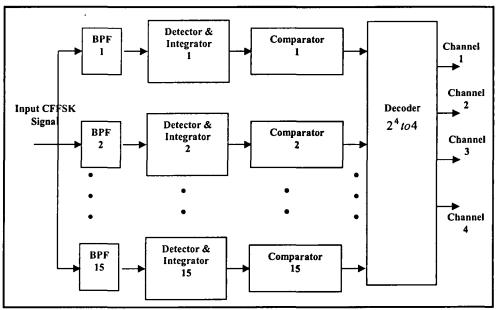

| Fig- 6.2 Block diagram of CMFSK based FHSS receiver    |                                             | 03/6 |

| Fig- 6.3 Block diagram of CMFSK system                 |                                             | 05/6 |

| Fig- 6.4                                               | P-Spice simulated waveforms of CMFSK system | 05/6 |

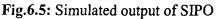

| Fig- 6.5                                               | Simulated output of SIPO                    | 06/6 |

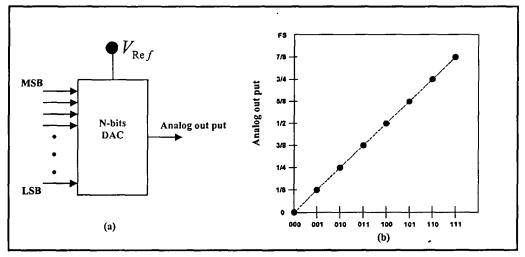

| Fig- 6.6                                               | Block diagram and characteristics of a DAC  | 07/6 |

---

|                                                                                                      | Fig- 6.7                                               | PIN diagram of DAC 701                                                            | 08/6         |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|--------------|

|                                                                                                      | Fig- 6.8 P-Spice simulated output from DAC             |                                                                                   | 08/6         |

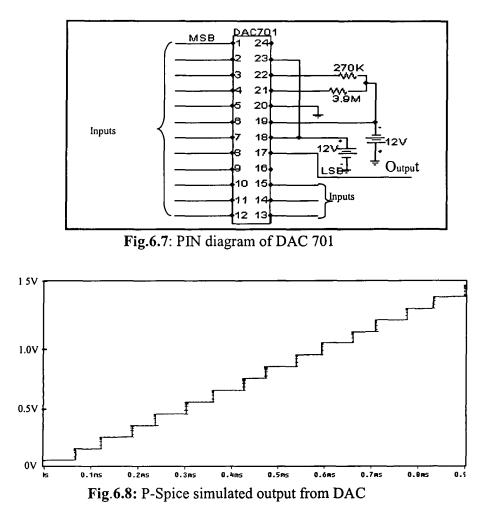

|                                                                                                      | Fig- 6.9 Pin diagram of VCO Max038                     |                                                                                   | 09/6         |

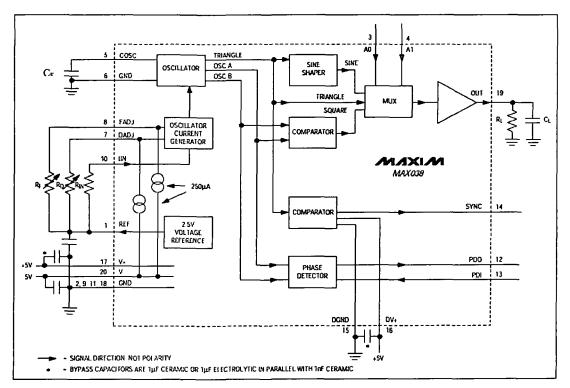

|                                                                                                      | Fig- 6.10 Internal circuit diagram of MAX 038 (VCO)    |                                                                                   | 10/6         |

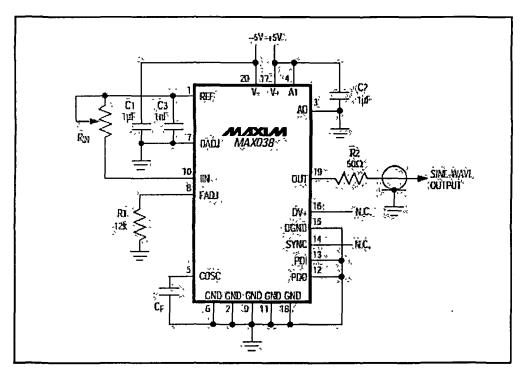

| Fig- 6.11 IC MAX038 as sinusoidal VCO                                                                |                                                        | 11/6                                                                              |              |

|                                                                                                      | Fig- 6.12Block diagram of CMFSK based FHSS transmitter |                                                                                   | 14/6         |

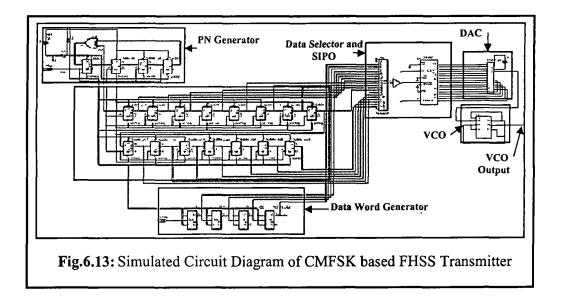

|                                                                                                      | Fig- 6.13                                              | Simulated Circuit diagram of CMFSK based FHSS Transmitter                         | 14/6         |

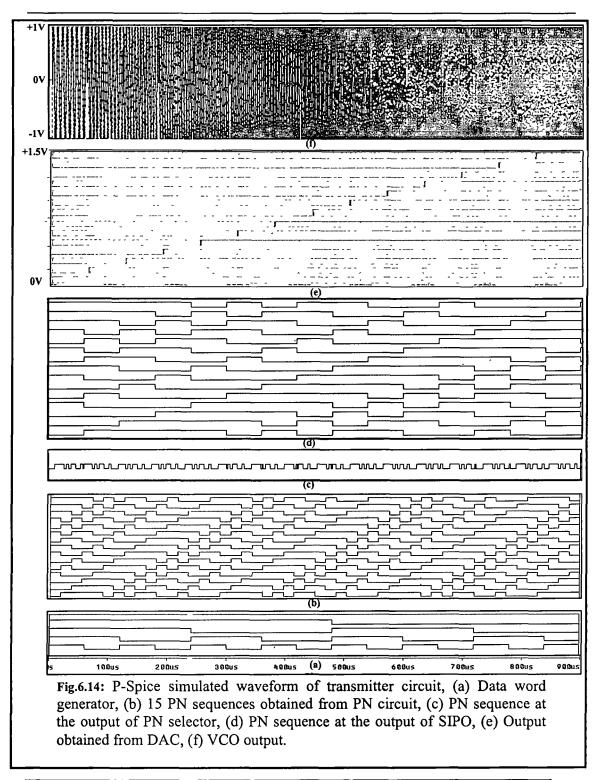

|                                                                                                      | Fig- 6.14                                              | P-Spice simulated waveform of FHSS transmitter                                    | 15/6         |

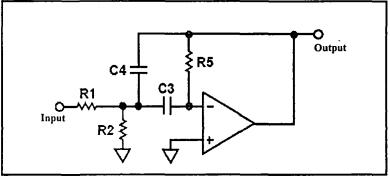

|                                                                                                      | Fig- 6.15                                              | Multiple Feedbacks BPF                                                            | 176          |

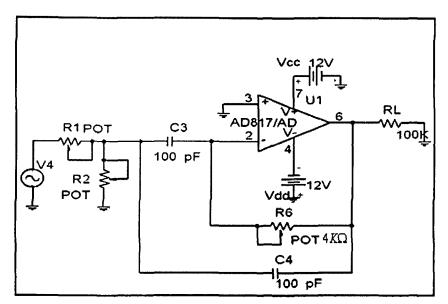

|                                                                                                      | Fig- 6.16                                              | Circuit diagram of BPF at 300 KHz                                                 | 18/6         |

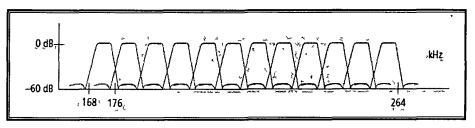

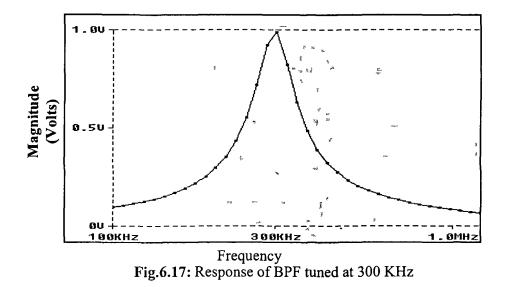

|                                                                                                      | Fig- 6.17                                              | Response of BPF tuned at 300 KHz                                                  | 18/6         |

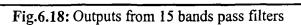

|                                                                                                      | Fig- 6.18                                              | Outputs from 15 bands pass filters                                                | 19/6         |

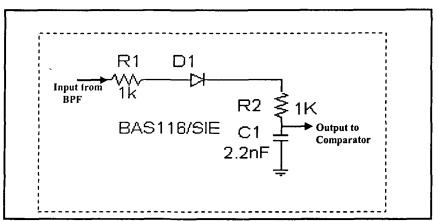

|                                                                                                      | Fig- 6.19                                              | Diode detector and integrator circuits                                            | 20/6         |

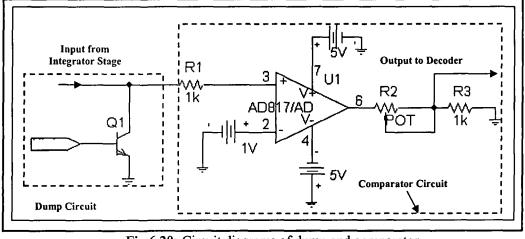

|                                                                                                      | Fig- 6.20                                              | Circuit diagrams of dump and comparator                                           | 21/6         |

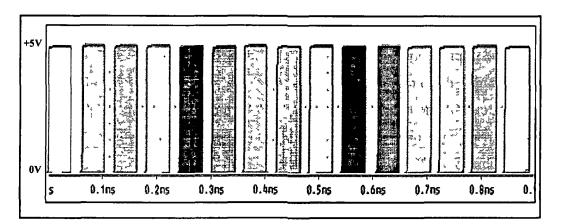

|                                                                                                      | Fig- 6.21                                              | Output pulses from 15 comparators                                                 | 22/6         |

| Fig- 6.22Simulated circuit diagram of decoder                                                        |                                                        | 23/6                                                                              |              |

| Fig- 6.23     Simulated encut diagram of decoder       Fig- 6.23     Simulated waveform from decoder |                                                        | 24/6                                                                              |              |

|                                                                                                      | Fig- 6.24                                              | Simulated block diagram of filter based CMFSK receiver                            | 25/6         |

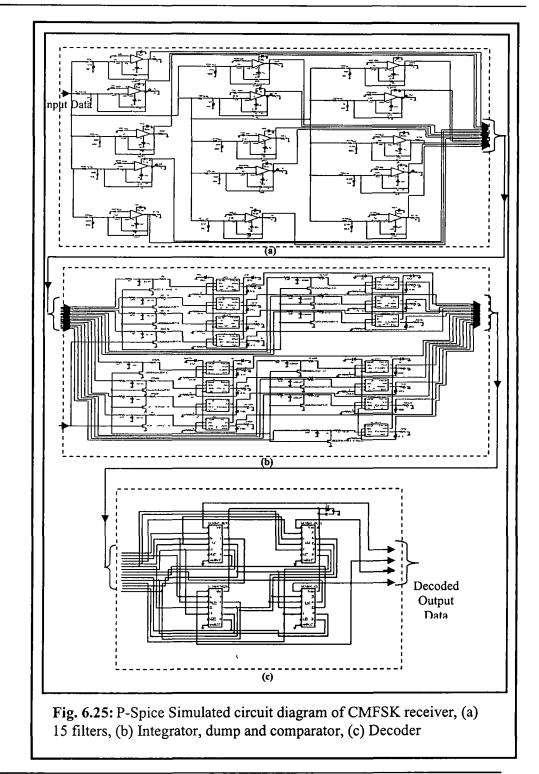

|                                                                                                      | Fig- 6.25                                              | P-Spice Simulated circuit diagram of CMFSK receiver                               | 26/6         |

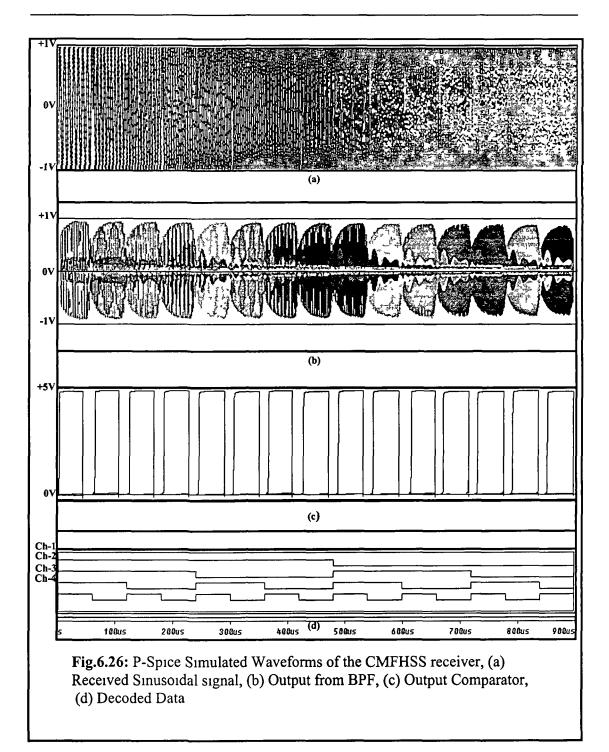

|                                                                                                      | Fig- 6.26                                              | P-Spice Simulated waveforms of the CMFHSS receiver                                | 27/6         |

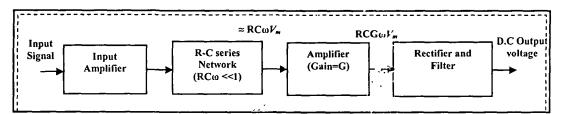

|                                                                                                      | Fig- 6.27                                              | Block diagram of the proposed FVC                                                 | 29/6         |

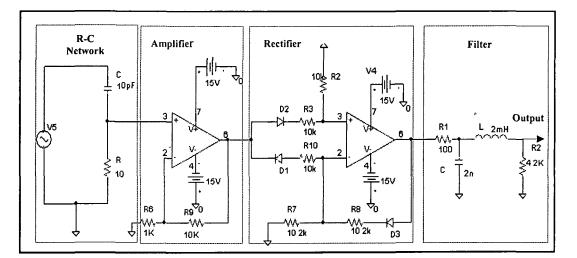

|                                                                                                      | Fig- 6.28                                              | Circuit diagram of the proposed FVC                                               | 30/6         |

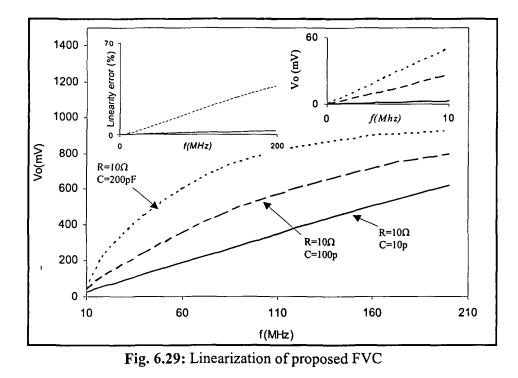

|                                                                                                      | Fig- 6.29                                              | Linearization of proposed FVC                                                     | 31/6         |

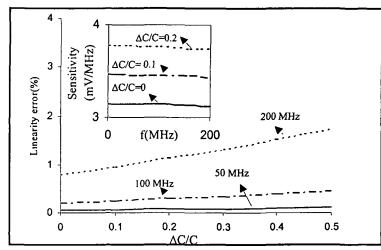

|                                                                                                      | Fig- 6.30                                              | Dependence of sensitivity and linearization on small change                       | 2016         |

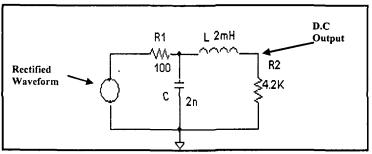

|                                                                                                      | Fig- 6.31                                              | of capacitance in RC network due to parasitic effect<br>Circuit diagram of filter | 32/6<br>33/6 |

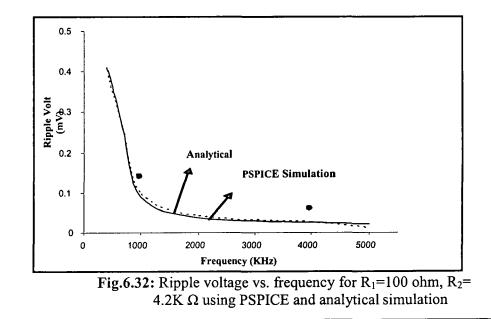

|                                                                                                      | Fig- 6.32                                              | Ripple voltage vs. frequency for $R_1=100$ ohm, $R_2=$                            |              |

|                                                                                                      |                                                        | 4.2K $\Omega$ using PSPICE and analytical simulation                              | 34/6         |

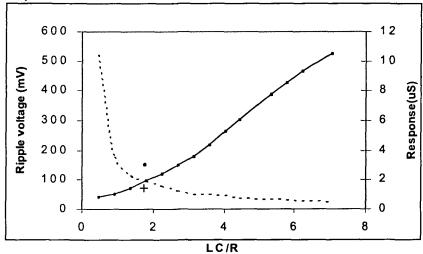

|                                                                                                      | Fig- 6.33                                              | Dependence of response time and ripple voltage on LC/ $R_1$                       | 36/6         |

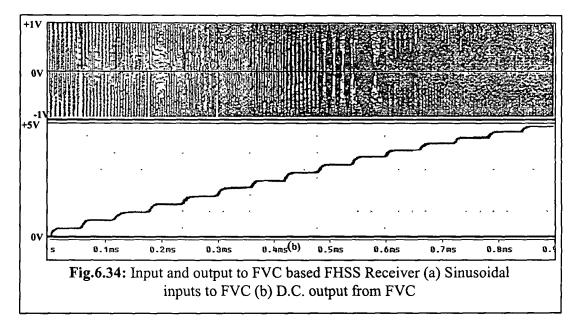

|                                                                                                      | Fig- 6.34                                              | Input and output to FVC based FHSS Receiver                                       | 37/6         |

|                                                                                                      |                                                        |                                                                                   |              |

| Fig- 6.35 Circuit diagram of comparator             |                                                         | 38/6 |

|-----------------------------------------------------|---------------------------------------------------------|------|

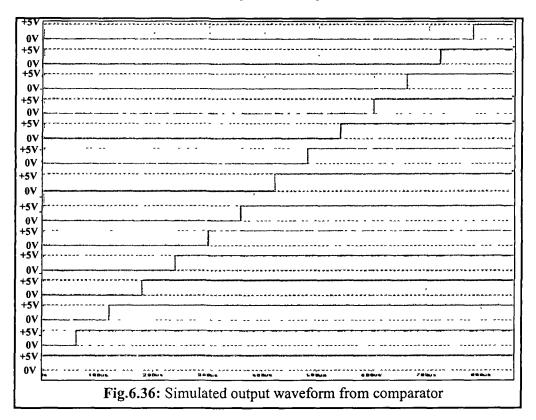

| Fig- 6.36 Simulated output waveform from comparator |                                                         | 38/6 |

| Fig- 6.37 IC HCF4532 for 16 to 4 Priority decoding  |                                                         | 40/6 |

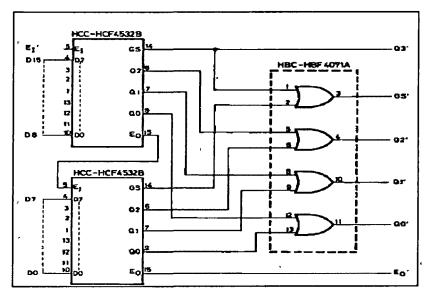

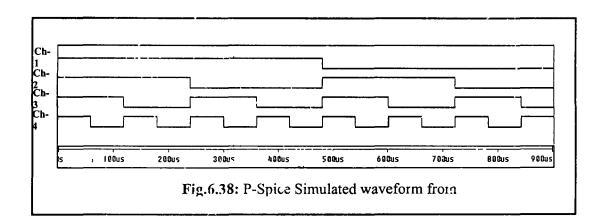

| Fig- 6.38                                           | P-Spice Simulated waveform from                         | 41/6 |

| Fig- 6.39                                           | Simulated Block diagram of receiver with proposed FVC   | 42/6 |

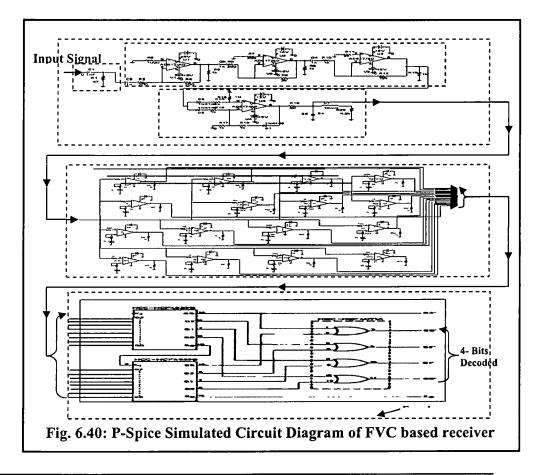

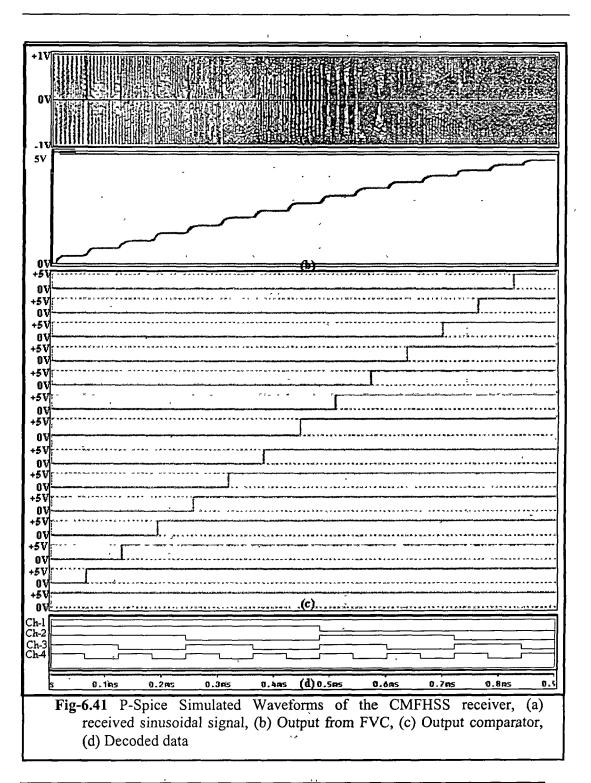

| Fig- 6.40                                           | P-Spice Simulated Circuit Diagram of FVC based receiver | 43/6 |

| Fig- 6.41                                           | P-Spice simulated waveforms of the CMFHSS receiver      | 44/6 |

#### <u>Chapter – 7</u>

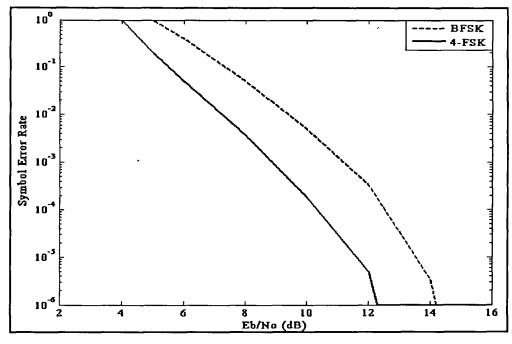

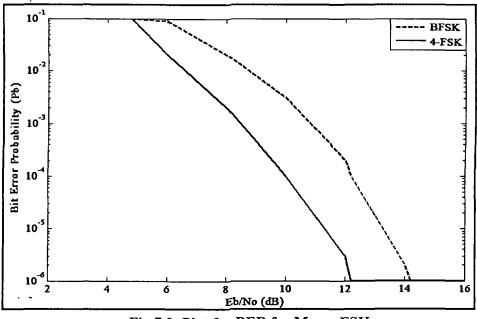

| Fig- 7.1                                                            | - 7.1 SER versus SNR, for M-ary 02                        |      |

|---------------------------------------------------------------------|-----------------------------------------------------------|------|

| Fig- 7.2                                                            | Fig- 7.2 Plot for BER for M-ary FSK system                |      |

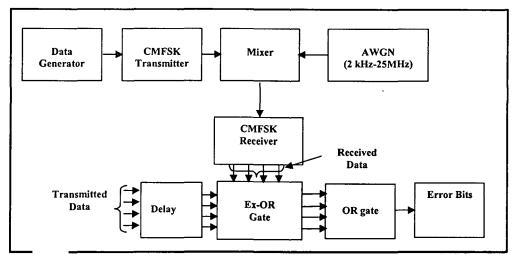

| Fig- 7.3                                                            | Fig- 7.3 Block diagram of SER simulation setup            |      |

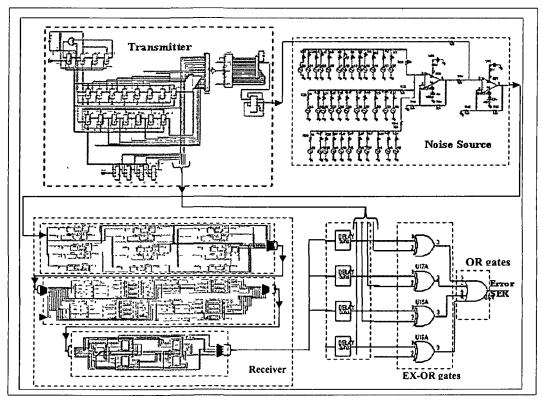

| Fig- 7.4                                                            | Fig- 7.4 Simulated Circuit diagram for SER estimation     |      |

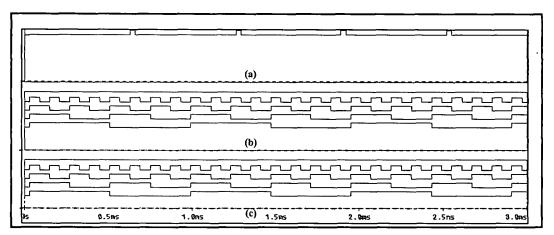

| Fig- 7.5                                                            | Fig- 7.5 Simulated waveform for SER with noise            |      |

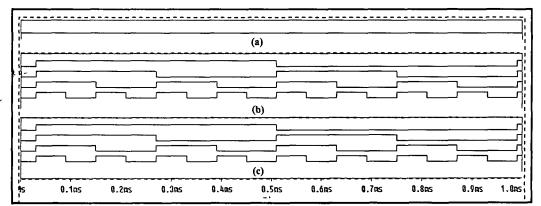

| Fig- 7.6                                                            | Fig- 7.6 Simulated waveforms for SER without noise        |      |

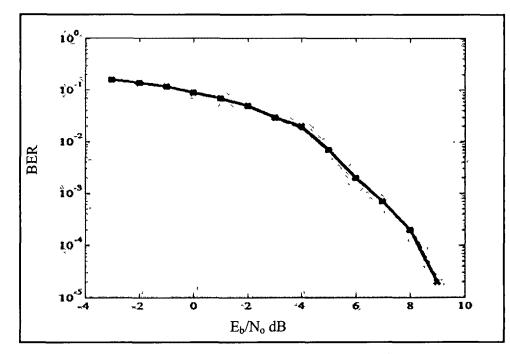

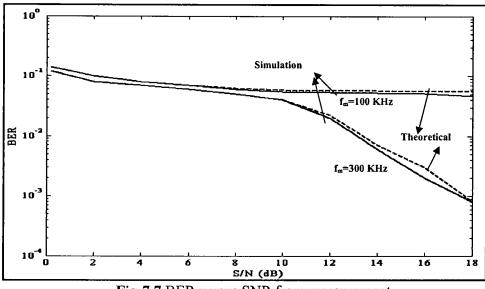

| Fig- 7.7                                                            | BER versus SNR from measurement                           | 08/7 |

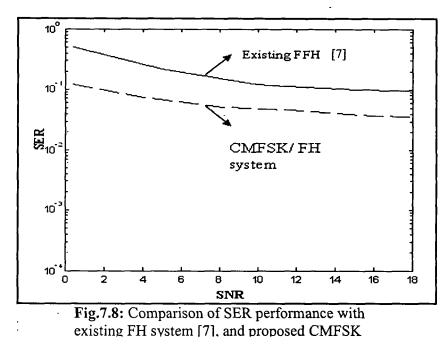

| Fig- 7.8 Comparison of SER performance with existing FH sy          |                                                           | d    |

|                                                                     | proposed CMFSK                                            | 09/7 |

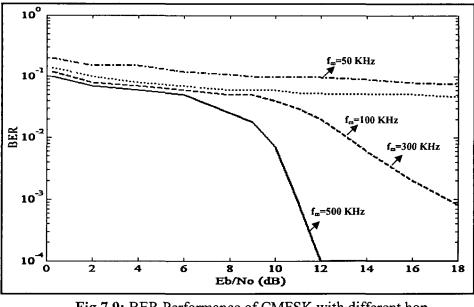

| Fig- 7.9                                                            | BER Performance of CMFSK with different hop               | 10/7 |

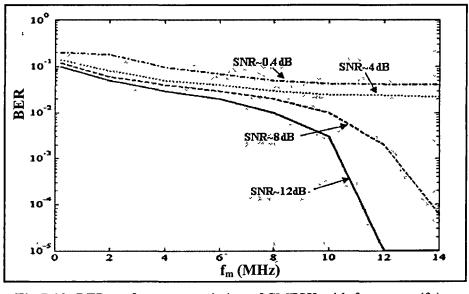

| Fig- 7.10 BER performance variation of CMFSK with frequency $(f_m)$ |                                                           | 10/7 |

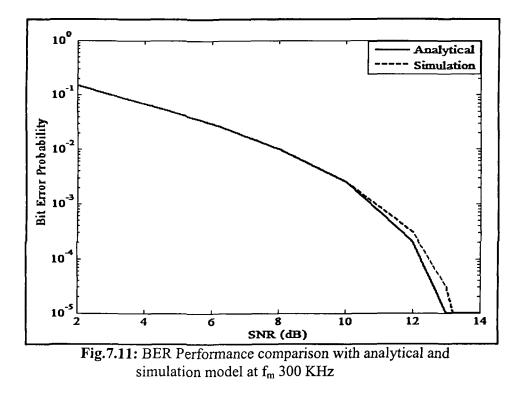

| Fig- 7.11                                                           | BER Performance comparison with analytical and simulation |      |

|                                                                     | model at f <sub>m</sub> 300 KHz                           | 12/7 |

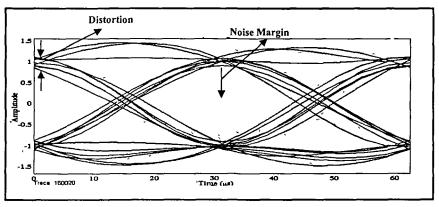

| Fig- 7.12                                                           | Eye diagram of CMFHSS receiver at 12 dB SNR               | 13/7 |

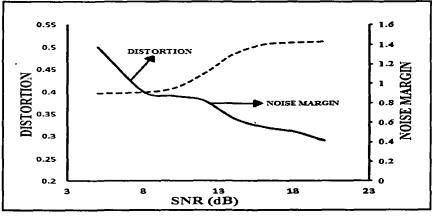

| Fig- 7.13                                                           | Plot for noise and distortion eye diagram                 | 13/7 |

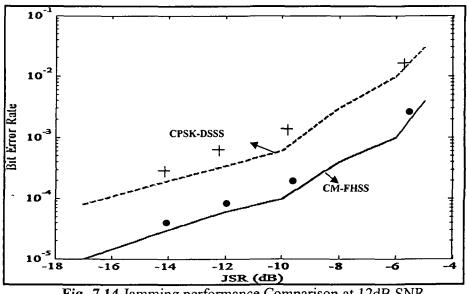

| Fig- 7.14                                                           | Jamming performance Comparison at 12dB SNR                | 14/7 |

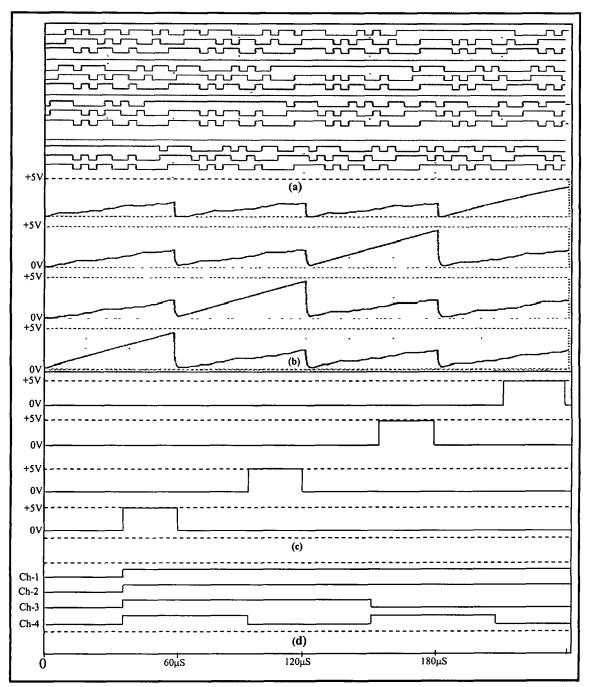

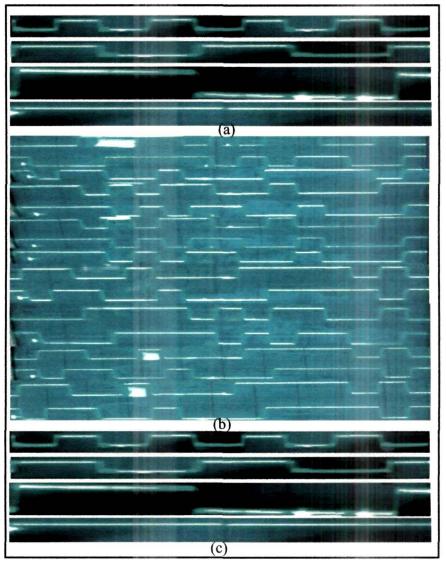

| Fig- 7.15                                                           | Experimental Setup for CMFSK based FHSS system            | 15/7 |

| Fig- 7.16                                                           | Oscilloscope traces of FVC based FHSS transceiver         | 16/7 |

|                                                                     |                                                           |      |

### **List of Abbreviations**

| adaptive channel allocation              |

|------------------------------------------|

| automatic gain control                   |

| amplitude shift keying                   |

| additive white Gaussian noise            |

| band pass filter                         |

| bit error rate                           |

| binary phase shift keying                |

| code shift keying                        |

| complementary metal oxide semiconductor  |

| code division multiple access            |

| code phase shift keying                  |

| code m-ary frequency hop spread spectrum |

| code division multiplexing               |

| digital to analog converter              |

| direct sequence spread spectrum          |

| differential binary phase shift keying   |

| frequency division multiplexing          |

| frequency hop spread spectrum            |

| frequency to voltage converter           |

| federal communications commission        |

| field programming gate array             |

| frequency hopping                        |

| frequency division multiple access       |

| global system for mobile                 |

| high pass filter                         |

| hierarchical cell structures             |

| jamming to signal ratio                  |

| low earth orbit                          |

| linear feedback shift register           |

|                                          |

#### List of Publications

#### Journal Papers

- 1. P.P. Sahu and M. Singh, "Multi channel frequency hopping spread spectrum signaling using code M-ary frequency shift keying." Computer and Electrical Engineering, (Elsevier), vol. 34, (2008), pp. 338-345.

- 2. Singh Mahipal, Sahu P. P. "Four channel transmitter and receiver using CPSK based direct sequence spread spectrum." International Journal HIT Transition on ECCN 2006: 1(1): 63-71.

- 3. P P Sahu and M Singh, "Multi-channel direct sequence spread spectrum signaling using Code Phase Shift Keying." Computers and Electrical Engineering, (Elsevier), Vol.35, 2009, pp. 218-226.

- 4. P. P. Sahu, M. Singh, and A. Baishya, "A Novel Versatile Precision Full-Wave Rectifier," IEEE Transactions on Instrumentation and Measurements, vol. 59, no. 10, pp. 2742-2746, Oct 2010.

- 5. P. P. Sahu, M. Singh, and A. Baishya, "New low-voltage full wave rectification technique without a diode" IET Circuits Devices Syst., vol. 5, issue 1, pp. 33-36, 2011.

- 6. M. Singh and P.P. Sahu "A Wideband Linear Sinusoidal Frequency to Voltage Converter with Fast Response Time" Procedia Engineering (Elsevier) vol. 64, pp.26-35 2013.

| LNA   | low noise amplifier             |

|-------|---------------------------------|

| LNA   | low noise amplifier             |

| MMSE  | minimum mean square error       |

| MIMO  | multiple-input multiple-output  |

| MLD   | maximum likelihood decoding     |

| MFSK  | m-ary frequency shift keying    |

| MSK   | minimum shift keying            |

| MSK   | minimum shift keying            |

| MAI   | multiple access interference    |

| PN    | pseudo-noise                    |

| PG    | processing gain                 |

| ΟΤΑ   | transconductance amplifier      |

| QPSK  | quadrature phase shift keying   |

| SER   | symbol error rate               |

| SDMA  | space division multiple access  |

| SIPO  | serial in parallel out          |

| SSMA  | spread spectrum multiple access |

| TDM   | time division multiplexing      |

| TDMA  | time division multiple access   |

| US DD | united states Digital Cellular  |

| VLSI  | very large scale integration    |

| VCO   | voltage control oscillator      |

|       |                                 |

# Chapter 1

Introduction

#### **1.1 Overview**

Over last two and half decades, the success of cellular system has revolutionized the wireless industry [1]. But the tremendous growth of wireless users [2] has put forth many challenges for wireless communications [3]-[4]. These challenges include accommodation of more users, needing for more spectrum, immunity to interferences from simultaneous users [5]-[8] etc. Engineers and researchers are putting many efforts to bridge these demand and supply gaps. Available spectrum is limited [9] which have posed growing pressure on wireless industry for efficient utilization [10] of available spectrum. Adding spectrum is not one of the enduring solutions to the above challenges. Therefore either new technology is to be evolved or existing technology to be modified for spectral efficiency. In this direction spread spectrum technique has emerged as one of the most popular tools to mitigate many issues [11] of wireless communications.

Since 1950, the spread spectrum systems have been developed, and initially, its applications were restricted for military to hide the data from enemy as an anti-jamming tactical communications [12]. In this technique the signal occupies the bandwidth [13]-[14], which is greater than the minimum necessary, for sending the information. Two methods, namely, (i) direct sequence spread spectrum (DSSS) [15] -[22] and (ii) frequency hopping spread spectrum (FHSS) [23] -[31] are used for spread spectrum communication. In the DSSS, fast pseudorandom sequence causes phase transitions in the carrier using different modulation techniques. In the FHSS system, pseudorandom sequences cause the carrier to hop from one frequency to another frequency.

To enhance system capacity/spectral efficiency, by accommodating a number of users on a single channel, different multiplexing techniques [32], namely, (i) time division multiplexing (TDM), (ii) frequency division multiplexing (FDM), (iii) code division multiplexing (CDM) and space division multiplexing (SDM) are used. In TDM, [33] successive intervals of time are assigned to the different uses. During these intervals the bits of information from all channels are transmitted in rotation. At the receiving terminal the pulses are sorted out according to their time of arrival, and diverted to their respective channel. In FDM [34], the total available bandwidth is divided into a series of non-overlapping sub bands, and each of them is dedicated to each user. As compared to TDM, FDM occupies more bandwidth; therefore it is not a bandwidth efficient system. CDM [35] is most bandwidth efficient technique and used for commercial applications by allowing several users to communicate simultaneously on common channel using pre-assigned code sequences. SDM [36]-[38] is more recently evolved technique for higher speed requirement of 4<sup>th</sup> and 5<sup>th</sup> generation. It utilizes the spatial separation of users. In these techniques all users are allowed to simultaneously share the common medium.

Further, the advancement in VLSI technology and signal processing [39]-[40] has played a dominating role to settle down some of the challenges of wireless communication by improving the quality of service, reduced power consumption, enhanced system capability and capacity [41]-[43]. Many signal processing techniques, such as filtering [44]-[45], equalization [46] -[49], detection [50] -[51], pulse shaping [52], demodulation [53] -[55], frequency to voltage converts (FVC) [56] -[58] etc., are evolved to enhance the performances of the communication devices.

This work discusses the design of multi-channeling (multiplexing) scheme using spread spectrum techniques for increasing channel capacity and performance evaluation of designed system. The proposed BPSK demodulation for demodulating has been studied for its performance. The sinusoidal FVC techniques have been studied for improving the performance of wireless FHSS communication systems and for wide band operation with very good linearity.

#### **1.2 Multi-channel Communications**

Since the origin of electronic communication there has been a requirement for providing simultaneous transmission of many messages using single transmission media [33] - [34]. Initially time division and frequency division multiplexing schemes were evolved

to increase the channel capacity [33]-[34]. The growth of users aggravated the capacity problem [59] and has caused an accelerating pressure on efficient use of bandwidth. The solution to the problem of efficient bandwidth utilization has emerged during 1950 and 1960, when researchers at Bell laboratories developed the cellular concept [60]. This concept exploits the fact that the power of transmitter signal fall off with distance therefore frequency reuse is possible at spatially separated location and hence more capacity. The founders of quality communication (QUALCOMM) developed CDMA technology for commercial cellular communications [1]-[61] to make even better use of the radio spectrum than other techniques for multiple accesses.

Code division multiple access (CDMA), is a spread spectrum technique in which each user is allocated signature code so that it can occupy same frequency spectrum simultaneously with the other users [15] -[16]. Therefore, CDMA systems can operate at much higher interference levels because of its interference resistance capability [61]. Along with this it provides multiple access capability with much higher capacity over other existing techniques like time division and frequency division multiplexing, high resistance to jamming, intentional interference therefore it is the most promising multiplexing technologies for current and future telecommunications services which has attracted it for future technology [35]-[36].

#### **1.3** Open Issues in Multi-channel Wireless Communication

The resources those make wireless communications possible are limited. The one of the most important resource is bandwidth (spectrum). At the same time, the growth in the number of wireless users [2] has caused pressure on efficient use of available bandwidth [3]-[4]. The initially developed wireless systems for telephony have used 120 KHz of bandwidth and immediately the bandwidth was cut down to 60 KHz to accommodate more number of users by improving the technology [1]. It has doubled the channel capacity but there was a long waiting list of more users demanding to have wireless access capability. Seeing the growing number of users, in 1989 an additional

spectrum of 10MHz was released to address these waiting users. With the advancement in very large scale integration (VLSI) and digital technology, in late 1991, the first US Digital Cellular (USDD) has supported 3 users in 30 KHz bandwidth and improved the channel capacity by three times. But this improvement in channel capacity was insufficient to cater all users. A better solution for capacity enhancement was proposed by QUALCOMM using spread spectrum based CDMA [61]. The rise in the number of wireless users will continue in future also due to population growth and technological advancement for more services. These factors are enhancing the pressure on existing technology. Further, the mounting pressure is not alone due to the exponential growth in the number of users; it is further accelerated by demand for high data rate, better quality of service, degradation due to interference, noises etc.

Therefore, these issues were developed since the origin of communication system because of a gap in demand and supply. The technological advancement is continuously trying to fill the gap by advanced signal processing techniques and will continue in future also. The main issues of multichannel wireless communications are bandwidth efficiency, better channel capacity and improvement in signal to noise ratio.

#### 1.4 Objectives

The main objectives of this dissertation are as follows:

- To design and simulate the proposed Code phase shift keying (CPSK) based DSSS transceiver for a multi channel using Sallen-Key filter.

- To design and simulate the proposed CPSK based DSSS receiver for a multi-channel using a proposed demodulator for improvement of BER performance under noise and jamming in comparison to the CPSK based DSSS transceiver using Sallen-Key filter

- To design and simulate code M-ary frequency shift keying (CMFSK) based FHSS transceiver for multi-channel using BPF.

- To design and simulate the CMFSK based FHSS receiver for multichannel using proposed sinusoidal FVC for improvement of BER performance under noise and jamming

#### **1.5 Contributions**

The conclusions of this research work along with key contributions are summarized as below:

- 1. Design and implementation of CPSK based DSSS transceiver for accommodating 4 users has been made. It has been found that without an increasing frequency band, numbers of users are increased by the same DSSS system and at the same time BER is less.

- 2. The proposed BPSK demodulator has been studied for DSSS system in order to reduce the BER further for DSSS.

- 3. Design and implementation of M-ary FSK based FHSS transceiver for accommodating 4 users has been studied and design along with performance evaluation.

4. R-C based FVC has been proposed for simplification of the FHSS circuit as the design of narrow band pass filter is critical requiring more order of the filter. It was also found that the proposed FVC provides linear frequency to voltage conversion over a wide range of frequency.